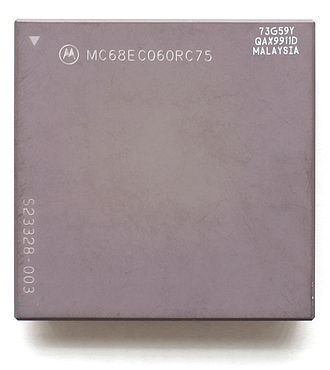

Motorola 68060

Der Motorola 68060 ist ein 32-Bit-Prozessor von Motorola (später Freescale, heute NXP). Er wurde 1994 als Nachfolger des Motorola 68040 veröffentlicht und ist der leistungsstärkste Prozessor der Motorola-68000er-Familie.

Architektur

BearbeitenDer Motorola 68060 (meistens einfach nur 060 genannt, sprich null-sechzig) ist kein einfaches Redesign des 68040, sondern wurde – basierend auf den Erfahrungen mit dem 68040 – komplett neu entwickelt. Es wurde eine zweite Einheit für Ganzzahlberechnungen hinzugefügt (Superskalarität) und eine Erweiterung für Ganzzahl-Multiplikationen, die nur zwei Takte pro Multiplikation benötigt. Die Einheit für Gleitkommaberechnungen (FPU) wurde durch eine schnellere Variante ersetzt, dabei wurden einige komplexere Funktionen des 68881/68882 nicht mit implementiert. Selbst gegenüber der FPU des 68040 wurden einige Funktionen gestrichen, was aber enorm zur Gesamt-Ausführungsgeschwindigkeit der 68060-FPU beiträgt (etwa Faktor 3,5). Die fehlende Funktionalität muss durch eine vom Hersteller bereitgestellte Softwarebibliothek emuliert werden. Weiterhin wurde eine Logik für Sprungvorhersagen (branch prediction) eingefügt. Der 68060 hat dadurch bei gleichem Takt etwa die zwei- bis dreifache Rechenleistung eines 68040. Die Entwicklungsmannschaft für den 68060 wurde von Joe Circello geleitet.

Der 68060 hat eine dem Intel Pentium ähnliche Architektur. Ein Teil der inneren Logik (einige Funktionsblöcke) arbeitet im Vergleich zum 68040 nicht mit der doppelten, sondern mit der dreifachen Busgeschwindigkeit. Das ist aber nicht mit der Taktverdopplung und -verdreifachung der DX-Prozessoren im PC-Bereich vergleichbar. Beide Prozessoren besitzen zwei superskalare in-order Pipelines. Jede Pipeline hat dabei jeweils einen Befehlsdekoder. Dieser zerlegt komplexe Maschinenbefehle in einfachere, bevor sie verarbeitet werden. Die interne Verarbeitung erfolgt in vier Stufen nach dem RISC-Prinzip. Der eigentliche Unterschied zum Pentium liegt in der nicht superskalar ausgeführten Gleitkommaeinheit (FPU) des 68060. Entweder können zwei Integer-Instruktionen und eine Branch-Instruktion oder eine Integer-, eine Gleitkomma- und eine Branch-Instruktion parallel verarbeitet werden. Allerdings können nicht alle Instruktionen unabhängig voneinander verarbeitet werden, so dass sich eine durchschnittliche IPC von etwa 1,3 ergibt. Der 68060 erreicht daher im Gleitkommabereich bei gleichem Takt nur etwa ein Drittel der Geschwindigkeit eines Pentium. Im Gegensatz dazu sind die ganzzahligen Multiplikations- und Bitschiebeoperationen (engl. „bit shifting“) wesentlich schneller. Außerdem kann der 68060 in der Adressierungseinheit einfache Befehle ausführen, so dass Resultate der Adressierungslogik zwei Rechenzyklen vor denen der ALU zur Verfügung stehen. Diese Art der Verarbeitung führt zu dem Zero-Cycle-Branch-Verhalten, das heißt, dass eine Verzweigung in der Regel keine Rechenzyklen kostet. Für diese Optimierungen wurde eine große Menge an kompiliertem kommerziellem Code analysiert. Darüber hinaus verfügt der 68060 gemäß der Harvard-Architektur über zwei MMUs, eine für Daten- und eine für Instruktionen-Paging. Im Integerbereich ist er mit seinen Vorgängern größtenteils binärkompatibel. Ein Teil der komplexeren Adressierungsarten des 68020/68030 werden allerdings nicht unterstützt. Die Kompatibilität im FPU-Bereich ist nur durch den Einsatz der Emulationsbibliothek gewährleistet. Die MMU wurde im Vergleich zum 68030 und 68040 in der Funktionalität reduziert, zum Beispiel werden nur noch Seitengrößen von 4 KiB und 8 KiB unterstützt.

Der 68060 ist der erste und einzige Vertreter der 68000er-Familie mit Energiesparfunktionen. Die CPU kann verschiedene Logikblöcke dynamisch je nach Auslastung herunter- oder herauftakten oder ganz deaktivieren. Auf diese Funktionen kann per Software zugegriffen werden.

Der 68060 war die letzte Entwicklung der Motorola 68000er-Familie. Motorola brach die Weiterentwicklung zugunsten der PowerPC-Prozessoren ab. Zuletzt wurde der 68060 in einigen späten Amiga-Modellen und deren Turbokarten-Erweiterungen eingesetzt. Auch gab es einige Atari-ST-Abkömmlinge, die von der letzten Generation Gebrauch machten. Der TOS-kompatible Medusa Hades mit 68060-Prozessor sowie die Erweiterungskarten CT60 und CT63 für den Atari Falcon gehörten dazu. Apple sowie ein Großteil der Unix-Welt stiegen nach dem 68040 auf RISC-basierende Prozessoren um. Der 68060 wurde mit einer Geschwindigkeit von 50 MHz eingeführt (basierend auf Motorolas 0,6-µm-Herstellungsprozess). Spätere Modelle erfuhren eine Reduzierung der Strukturbreite auf 0,42 µm und konnten so mit 66 MHz, teilweise sogar mit 75 MHz betrieben werden. Einige der EC- und LC-Varianten wurden sogar mit 80 MHz oder gar 90 MHz betrieben. Die 0,42-µm-Prozessoren waren sehr selten, da sich Motorola inzwischen auf seine PowerPC-Prozessoren konzentrierte.

Varianten

Bearbeiten- 68060 – vollständige CPU mit FPU und MMU

- 68LC060 – deaktivierte FPU, MMU vorhanden

- 68EC060 – FPU und MMU deaktiviert

Technische Merkmale

Bearbeiten| Arbeitsfrequenzen | 50 MHz, 60 MHz, 66 MHz, 75 MHz |

| Betriebsspannung | Vcore 3,3 V I/O 5 V |

| Arbeitstemperatur | −40 °C bis 70 °C (85 °C bei aktuelleren Masken) |

| Herstellungsprozess | static-CMOS 0,6 μm und später 0,42 μm |

| Bauweise | PGA 206 (kompatibel zum 68040), TBGA 304 (31 × 31 × 1,7 mm³; 1,27 mm Pitch) |

| Datenbus | 32 Bit |

| Adressbus | 32 Bit |

| Befehlssatz | CISC (intern ähnlich der RISC-Arbeitsweise durch Zerlegung von Macro-Ops in Micro-Ops) |

| Cache | 8 KiB DCache (4-fach assoziativ) 8 KiB ICache (4-fach assoziativ) 64 Entry ATC MMU Buffer (4-fach assoziativ) 96 Byte FIFO Instruction Buffer 256 Entry Branch Cache |

| Register |

|

| Transistoren | ≈ 2,5 Mio. |

| Performance | 66 MHz: ≈88 MIPS ≈36 MFLOPS 75 MHz: ≈110 MIPS |

Trivia

Bearbeiten- LC und EC sind Varianten der CPU, bei denen während des Herstellungsprozesses auf dem Die Fehler innerhalb der FPU- und/oder MMU-Einheit festgestellt wurden. Um die Ausbeute der Fertigung zu erhöhen, wurden die betroffenen Einheiten gezielt deaktiviert und die CPU mit entsprechend reduziertem Funktionsumfang preiswerter verkauft.

- Die Viper 1260 (eine Amiga 1200-Turbokarte) nutzte einen 68060 mit 50 MHz übertaktet auf 56 MHz.

- Die Apollo 1260 (eine Amiga 1200-Turbokarte) lässt sich mit einem 68060 Rev.6 bis 80 MHz takten.

- Die CT60 (eine Atari-Falcon-Erweiterungskarte) erreicht mit Prozessoren der Rev.6 Taktraten von 90 MHz bis über 100 MHz.