(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第3692810号 (P3692810)

(45) 発行日 平成17年9月7日(2005.9.7)

(24) 登録日 平成17年7月1日 (2005.7.1)

(51) Int.C1.<sup>7</sup>

FI

HO1L 21/60

HO1L 21/60 311W HO1L 21/60 311R

請求項の数 10 (全 10 頁)

(21) 出願番号 特願平11-11717

(22) 出願日 平成11年1月20日 (1999.1.20)

(65) 公開番号 特開2000-216200 (P2000-216200A)

(43) 公開日 平成12年8月4日 (2000.8.4) 審査請求日 平成15年8月8日 (2003.8.8) (73)特許権者 000002369

セイコーエプソン株式会社

東京都新宿区西新宿2丁目4番1号

||(74)代理人 100090479

弁理士 井上 一

(74)代理人 100090387

弁理士 布施 行夫

|(74)代理人 100090398

弁理士 大渕 美千栄

|(72)発明者 橋元 伸晃

長野県諏訪市大和3丁目3番5号 セイコ

ーエプソン株式会社内

審査官 池渕 立

最終頁に続く

(54) 【発明の名称】半導体装置及びその製造方法、回路基板並びに電子機器

## (57)【特許請求の範囲】

### 【請求項1】

複数のスルーホールが形成され、一方の面で各々の前記スルーホールに対して電気的に接続された配線が形成された基板を用意する第1工程と、

前記配線に対して無電解メッキを施す第2工程と、

前記基板に樹脂を設け、その後、前記基板に少なくとも一つの半導体チップをフェースダウン実装し、前記配線における前記基板との非接触面全面を前記樹脂で被覆する第3工程と、

前記半導体チップよりも外側であって前記配線を避ける位置で前記基板を打ち抜く第4 工程と、

を含む半導体装置の製造方法。

### 【請求項2】

請求項1記載の半導体装置の製造方法において、

前記第3工程で、前記樹脂としての接着剤に導電粒子が含有されてなる異方性導電材料を介して前記半導体チップをフェースダウン実装し、前記配線における前記基板との非接触面全面を覆って前記異方性導電材料を設けることで前記配線を被覆する半導体装置の製造方法。

## 【請求項3】

請求項1又は請求項2記載の半導体装置の製造方法において、

前記スルーホール内の導電部材を介して前記配線に電気的に導通する複数の外部端子を

20

30

40

設ける工程をさらに含む半導体装置の製造方法。

#### 【請求項4】

請求項3記載の半導体装置の製造方法において、

それぞれの前記配線の一方の端部は前記半導体チップのいずれかの電極と接合され、他方の端部は前記スルーホール内の導電部材を介していずれかの前記外部端子と接合される 半導体装置の製造方法。

### 【請求項5】

請求項1から請求項4のいずれかに記載の半導体装置の製造方法において、

前記第3工程で前記基板に複数の半導体チップをフェースダウン実装し、前記第4工程でそれぞれの半導体チップごとに前記基板を打ち抜く半導体装置の製造方法。

### 【請求項6】

請求項5記載の半導体装置の製造方法において、

前記基板は、テープキャリアである半導体装置の製造方法。

### 【請求項7】

複数のスルーホールが形成され、一方の面で各々の前記スルーホールに対して電気的に接続されて無電解メッキが施されている配線が形成された基板と、

接着剤に導電粒子が含有されてなり、前記配線における前記基板との非接触面全面を覆う異方性導電材料と、

前記異方性導電材料を介して前記基板にフェースダウン実装された半導体チップと、 前記スルーホール内の導電部材を介して前記配線に電気的に導通する複数の外部端子と

を含む半導体装置。

### 【請求項8】

請求項7記載の半導体装置において、

それぞれの前記配線の一方の端部は前記半導体チップのいずれかの電極と接合され、他方の<u>端部</u>は前記スルーホール内の導電部材を介していずれかの前記外部端子と接合される 半導体装置。

### 【請求項9】

請求項7又は請求項8記載の半導体装置が搭載された回路基板。

### 【請求項10】

請求項7又は請求項8記載の半導体装置を備える電子機器。

## 【発明の詳細な説明】

### [0001]

## 【発明の属する技術分野】

本発明は、半導体装置及びその製造方法、回路基板並びに電子機器に関する。

### [0002]

### 【発明の背景】

CSP(Chip Scale/ Size Package)型の半導体装置の中で、1つの形態として、半導体チップを基板に対してフェースダウン実装(フリップチップ接続)した構造が知られている。基板としてテープを採用し、これに複数の半導体装置に対応する複数の配線パターンを形成しておき、半導体チップの実装後に各半導体装置に応じてテープを打ち抜くことで、生産性を向上することができる。それぞれの配線パターンは電解メッキを施すために相互に導通しており、テープを打ち抜くときに配線パターンも切断される。

## [0003]

したがって、完成した半導体装置の基板の端面には、配線パターンの切断面が露出する。 そして、この露出した切断面から半導体チップの電極に向けて腐食が進むことがあり得る。 また、配線パターンを構成する個々の配線間隔の狭ピッチ化によって、露出した切断面 に例えば導電性の異物が介在する等によりショートが生じて機能が損なわれることもあり 得る。

## [0004]

20

30

40

50

特に、CSP型の半導体装置のように小型化が進めば進むほどこれらの課題を解決するための策を講じる必要性が高くなる。

### [0005]

本発明は、上述したような課題を解決するものであり、その目的は、半導体装置の側面に配線の端面を露出させないことが可能な半導体装置及びその製造方法、<u>回</u>路基板並びに電子機器を提供することにある。

### [0006]

## 【課題を解決するための手段】

(1) 本発明に係る半導体装置の製造方法は、複数のスルーホールが形成され、一方の面で各々の前記スルーホールに対して電気的に接続された配線が形成された基板を用意する第1工程と、

前記配線に対して無電解メッキを施す第2工程と、

前記基板に樹脂を設け、その後、前記基板に少なくとも一つの半導体チップをフェース ダウン実装し、前記配線における前記基板との非接触面全面を<u>前記</u>樹脂で被覆する第3工 程と、

前記半導体チップよりも外側であって前記配線を避ける位置で前記基板を打ち抜く第4 工程と、

を含む。

### [0007]

本発明によれば、無電解メッキを適用して配線にメッキを施すことができる。また、第4 工程で配線を避ける位置で基板が打ち抜かれるので、配線が切断されることがなく、切断 面が露出することもない。なお、配線は、第3工程で樹脂にて被覆される。こうして、得 られた半導体装置によれば、配線の端面が露出していないので、湿気の進入経路を遮断す ることができる。また、電解メッキを施すときには必要であったメッキリードがないので 、配線の設計効率が向上して多ピン(多グリッド)の半導体装置(特にCSP)を容易に 設計することができる。さらに、メッキリードがないので、不要なリードに信号を伝える ことがなく、伝送特性が向上する。

### [00008]

(2)この製造方法において、

前記第3工程で、前記樹脂としての接着剤に導電粒子が含有されてなる異方性導電材料を介して前記半導体チップをフェースダウン実装し、前記配線における前記基板との非接触面全面を覆って前記異方性導電材料を設けることで前記配線を被覆してもよい。

[0009]

これによれば、半導体チップを簡単に実装することができ、実装するときに同時に配線の 被覆も可能になる。

[0010]

(3)この製造方法において、

前記スルーホール内の導電部材を介して前記配線に電気的に導通する複数の外部端子を設ける工程をさらに含んでもよい。

[0011]

(4)この製造方法において、

それぞれの前記配線の一方の端部は前記半導体チップのいずれかの電極と接合され、他方の端部は前記スルーホール内の導電部材を介していずれかの前記外部端子と接合されてもよい。

### [0012]

こうすることで、配線の両端に、半導体チップの電極と外部端子とが接合されるので、信号の伝送が必要な経路のみに配線が形成されることになり、伝送特性が向上する。

### [0013]

(5)この製造方法において、

前記第3工程で前記基板に複数の半導体チップをフェースダウン実装し、前記第4工程で

30

40

50

それぞれの半導体チップごとに前記基板を打ち抜いてもよい。

[0014]

こうすることで、半導体装置の生産性が向上する。

[0015]

(6)この製造方法において、

前記基板は、テープキャリアであってもよい。

[0016]

(7) 本発明に係る半導体装置は、上記方法により製造される。

[0017]

(8) 本発明に係る半導体装置は、複数のスルーホールが形成され、一方の面で各々の前記スルーホールに対して電気的に接続されて無電解メッキが施されている配線が形成された基板と、

接着剤に導電粒子が含有されてなり、前記配線における前記基板との非接触面全面を覆う 異方性導電材料と、

前記異方性導電材料を介して前記基板にフェースダウン実装された半導体チップと、 前記スルーホール内の導電部材を介して前記配線に電気的に導通する複数の外部端子と、 を含む。

[0018]

本発明によれば、配線の端面が露出していないので、湿気の進入経路を遮断することができる。また、電解メッキを施すときには必要であったメッキリードがないので、配線の設計効率が向上して多ピン化(多グリッド化)が可能である。さらに、メッキリードがないので、不要なリードに信号を伝えることがなく、伝送特性が向上する。

[0019]

(9)この半導体装置において、

それぞれの前記配線の一方の端部は前記半導体チップのいずれかの電極と接合され、他方の端部は前記スルーホール内の導電部材を介していずれかの前記外部端子と接合されてもよい。

[0020]

こうすることで、配線の両端に、半導体チップの電極と外部端子とが接合されるので、信号の伝送が必要な経路のみに配線が形成されることになり、伝送特性が向上する。

[0023]

(10)本発明に係る回路基板には、上記半導体装置が搭載されている。

[0024]

(11) 本発明に係る電子機器は、上記半導体装置を備える。

[0025]

【発明の実施の形態】

以下、本発明の好適な実施の形態について図面を参照して説明する。

[0026]

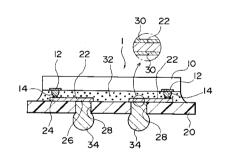

図1は、本発明の実施の形態に係る半導体装置を示す図である。この半導体装置1は、半導体チップ10と、基板20と、を含む。半導体チップ10の平面形状が矩形(正方形又は長方形)である場合には、少なくとも一辺(対向する二辺又は全ての辺を含む)に沿って、半導体チップ10の一方の面(能動面)に複数の電極12が形成されている。電極12には、ハンダボール、金ワイヤーボール、金メッキなどによってバンプ14が設けられている。電極12自体がバンプの形状をなしていてもよい。電極12とバンプ14との間にバンプ金属の拡散防止層として、ニッケル、クロム、チタン等を付加してもよい。

[0027]

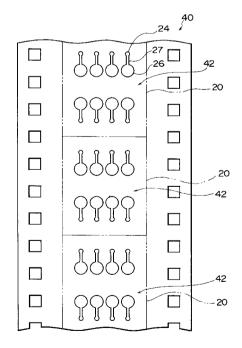

基板 2 0 の全体形状は特に限定されず、矩形、多角形、あるいは複数の矩形を組み合わせた形状のいずれであってもよいが、半導体チップ 1 0 の平面形状の相似形とすることができる。基板 2 0 の厚みは、その材質により決まることが多いが、これも限定されない。基板 2 0 は、有機系又は無機系のいずれの材料から形成されたものであってもよく、これら

の複合構造からなるものであってもよいが、打ち抜けることが好ましい。有機系の材料から形成されたテープ状のフレキシブル基板を打ち抜いて基板 2 0 を形成することができる。例えば、図 3 に示すキャリアテープ 4 0 を打ち抜いて、複数の基板 2 0 が得られる。

## [0028]

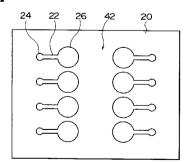

図2は、図1に示す半導体装置の基板の平面図である。図1及び図2に示すように、基板20の一方の面には、複数の配線(リード)22が形成されて、配線パターン42を構成している。複数の配線22のうちの少なくとも一つ又は全部は、他の配線22と電気的に導通しておらず、電気的に独立している。あるいは、複数の配線22のうち、半導体チップ10の電源やグランドなどに接続される共通の配線などは、ランド同士が接続されていてもよい。それぞれの配線22の両端には、ランド部24、26が形成されている。ランド部24、26は、その間を接続する部分よりも大きい幅を有するように形成されていることが多い。一方のランド部24を基板20の、最終的な製品としての半導体装置の端部に近い位置に形成し、他方のランド部26を基板20の中央に近い位置に形成してもよい

### [0029]

基板 2 0 には、複数のスルーホール 2 8 が形成されている。それぞれのスルーホール 2 8 上を、いずれかの配線 2 2 が通る。配線 2 2 の端部がスルーホール 2 8 上に位置してもよい。配線 2 2 の端部にランド部 2 6 が形成されている場合には、ランド部 2 6 がスルーホール 2 8 上に位置する。

## [0030]

配線22には、メッキ層30が形成されている。配線22を銅で形成し、メッキ層30を ニッケル、金、ハンダ又はスズで形成することができる。メッキ層30を形成することで 、導電性が確保される。具体的には、外部端子との良好なハンダ付けが可能になり、配線 22の表面の酸化が防止され、バンプとの電気的な接続抵抗が低下する。

### [0031]

それぞれの配線 2 2 は、電気的に独立しているので、無電解メッキを施すことでメッキ層 3 0 を形成することができる。メッキ層 3 0 は、配線 2 2 における基板 2 0 との接着面とは反対側の表面に形成される。メッキ層 3 0 は、配線 2 2 における基板 2 0 との接着面であってスルーホール 2 8 の内側の領域にも形成され、この領域はランド部 2 6 の一部ともなり得る。さらに、メッキ層 3 0 は、配線 2 2 における側面及び先端面にも形成される。 【 0 0 3 2 】

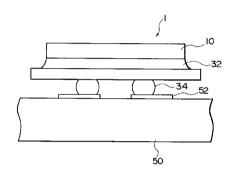

半導体チップ10は、基板20に対してフェースダウン実装される。半導体チップ10のバンプ14と、基板20に形成された配線22と、が電気的に接続される。配線22にはメッキ層30が形成されているので、良好な電気的接続が得られる。配線22にランド部24、26が形成される場合には、一方のランド部24とバンプ14とが電気に接続される。電気的接続の手段として、樹脂からなる接着剤に導電粒子が含有されてなる異方性導電材料32を使用してもよい。その場合には、導電粒子が配線22とバンプ14との間に介在して電気的な導通が図られる。異方性導電材料32は、異方性導電膜又は異方性導電接着剤であってもよい。

### [0033]

異方性導電材料32が使用される場合には、これによって配線22における基板20との接着面とは反対側の表面、側面及び先端面が覆われる。異方性導電材料32が使用されない場合には、アンダーフィル材などの樹脂によって、配線22における基板20との接着面とは反対側の表面、側面及び先端面を覆う。配線22を覆う材料は、基板20の一方の面の全面を覆ってもよい。

## [0034]

配線22には、外部端子34が電気的に接続されている。外部端子34は、ハンダボールであることが多いが、メッキ、導電樹脂などの導電性突起であってもよい。外部端子34は、スルーホール28内の導電部材を介して配線22に電気的に接続することができる。スルーホール28内にハンダなどの導電部材を充填して、配線22に直接的に外部端子3

20

30

40

4を設けてもよい。特に、配線22の一方の端部に半導体チップの電極12を接続し、配線22の他方の端部に外部端子34を接続すれば、両者間の電気的な経路にのみ配線22が形成されることになり、信号の伝送特性が向上する。すなわち、設計上、電気的経路的外の余分な配線パターン、例えばメッキリードなどが全く不要になるため、信号の反射的反射が高います。配線22には、スルーホール28によって露出する部分にもメッキョーが形成されているので、外部端子34と配線22との良好な電気的接続が得られる。るいは、スルーホール28を介して配線22に電気的に接続される第2の配線を、基板20の他方の面に形成して、その第2の配線に外部端子を設けてもよい。この場合には、多のの他方の面に形成して、その第2の配線に外部端子を設けてもよい。この場合には、多極をでは、両面に配線が形成されるので両面基板である。さらに、基板20として、多層をでは、両面に配線が形成されるので両面を設けてもよい。最終の他が表面をでは、表面の配線によりが、最終でできる。とができる。

#### [0035]

以上の説明は、異方性導電材料を用いる方式のフェースダウン型接合について述べてきたが、この方式のフェースダウン型接合に限られることはなく、ハンダバンプ付きの半導体チップを加熱(必要に応じて加圧)する方式や、金バンプ付きの半導体チップを加熱・加圧(必要に応じて超音波接合)する方式や、樹脂の硬化収縮力を利用した方式のフェースダウン接合にも本発明を適用することができる。

### [0036]

また、上述してきた形態では、配線 2 2 上の全ての部分が無電解メッキされているが、必要に応じて接続に関与する部分のみに無電解メッキを施し、それ以外の部分を無電解メッキなしでレジストなどの樹脂で覆っても良い。

### [0037]

図1には、配線22が半導体チップ10の搭載領域内にのみ形成されて外部端子34が半導体チップ10の搭載領域内にのみ設けられたFAN-IN型の半導体装置が示されているが、これに限定されるものではない。例えば、配線22を半導体チップ10の外にまで引き出して半導体チップ10の搭載領域外にのみ外部端子34が設けられたFAN-OUT型の半導体装置や、これにFAN-IN型を組み合わせたFAN-IN/OUT型の半導体装置にも本発明を適用することができる。いずれの場合であっても、配線22に無電解メッキを施して樹脂によって被覆し、そのさらに外側を半導体装置の外形となるように打ち抜けばよい。なお、FAN-OUT型又はFAN-IN/OUT型の半導体装置では、配線を被覆する樹脂によって、半導体チップの外側にスティフナを貼り付けても良い。

### [0038]

以上述べてきた形態の他に、半導体チップの実装前に予め、半導体装置の外形位置の一部 好ましくは半分以上に、一つ好ましくは複数の穴(例えば長穴)を形成しておき、半導体 チップの実装後に、外形位置の残りの部分(例えば複数の穴の間の部分)を打ち抜いても よい。

### [0039]

本実施の形態は、上記のように構成されており、以下その製造方法について説明する。

### [0040]

## (第1工程)

上述した基板 2 0 は、それよりも大きい基板(基材)を打ち抜いて形成することができる。本実施の形態では、図 3 に示すテープキャリア 4 0 を用意する。テープキャリア 4 0 には、打ち抜きによって、複数の基板 2 0 を得られるようになっている。すなわち、テープキャリア 4 0 には、複数の基板 2 0 に対応する複数の配線パターン 4 2 を構成する複数の配線 2 2 が形成されている。テープキャリア 4 0 は、配線 2 2 にメッキ層 3 0 が形成されていない点を除き、複数の基板 2 0 (図 1 及び図 2 参照)の構成を含む。

## [0041]

50

40

20

30

40

50

### (第2工程)

次に、テープキャリア40に形成された配線22に、無電解メッキを施して、図1に示すようにメッキ層30を形成する。

### [0042]

### (第3工程)

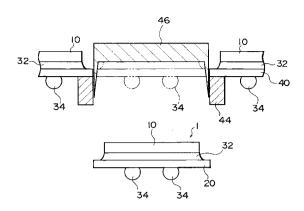

テープキャリア40に形成されたそれぞれの配線パターン42に、半導体チップ10をフェースダウン実装する。例えば、図1に示すように、異方性導電材料32を使用することができる。異方性導電材料32は、半導体チップ10における電極12が形成された面に予め設けておいても良いし、テープキャリア40における配線22が形成された面に予め設けておいても良い。個々の配線パターン42ごとに覆うように異方性導電材料32を設けてもよいし、複数の配線パターン42を覆うように異方性導電材料32を設けてもよい

## [0043]

そして、全ての配線 2 2 の表面、側面及び先端面を被覆する。異方性導電材料 3 2 が使用される場合には、これを設けることで同時に被覆してもよい。あるいは、他の材料によって被覆しても良い。

### [0044]

また、図1に示す外部端子34を設ける。外部端子34の詳細は、本実施の形態で説明した通りである。

### [0045]

こうして、図4に示すように、テープキャリア40に複数の半導体チップ10が実装されて、複数の半導体装置1が一体化された半導体装置アッセンブリが得られる。

### [0046]

### (第4工程)

図4に示すように、それぞれの半導体チップ10よりも外側であって、配線22を避ける位置で、テープキャリア40を打ち抜く。打ち抜き形状は、特に限定されないが、半導体チップ10の平面形状の相似形としてもよい。打ち抜きのために、切断治具44、46を使用することができる。こうして、半導体装置1を連続して製造することができる。

## [0047]

本実施の形態によれば、予め電気的に独立した状態で複数の配線22を形成してあるので、無電解メッキを適用して配線22にメッキ層30を形成することができる。また、第4 工程で配線22を避ける位置でテープキャリア40が打ち抜かれるので、配線22が切断されることがなく、切断面が露出することもない。こうして、得られた半導体装置1によれば、配線22の端面が露出していないので、湿気の進入経路を遮断することができ、切断面を被覆するために半導体装置の側面に樹脂などを設けなくてもよい。また、電解メッキを施すときには必要であったメッキリードがないので、配線22の設計効率が向上して多ピン(多グリッド)の半導体装置(特にCSP)を容易に設計することができる。さらに、メッキリードがないので、不要なリードに信号を伝えることがなく、伝送特性が向上する。

### [0048]

図5には、本実施の形態に係る半導体装置1を実装した回路基板50が示されている。回路基板50には例えばガラスエポキシ基板等の有機系基板を用いることが一般的である。回路基板50には例えば銅からなる配線パターン52が所望の回路となるように形成されていて、それらの配線パターンと半導体装置1の外部端子34とを機械的に接続することでそれらの電気的導通を図る。

## [0049]

そして、本発明を適用した半導体装置1を有する電子機器60として、図6には、ノート型パーソナルコンピュータが示されている。

### [0050]

なお、上記本発明の構成要件「半導体チップ」を「電子素子」に置き換えて、半導体チッ

プと同様に電子素子(能動素子か受動素子かを問わない)を、基板に実装して電子部品を 製造することもできる。このような電子素子を使用して製造される電子部品として、例え ば、抵抗器、コンデンサ、コイル、発振器、フィルタ、温度センサ、サーミスタ、バリス タ、ボリューム又はヒューズなどがある。

### 【図面の簡単な説明】

- 【図1】図1は、本発明の実施の形態に係る半導体装置を示す図である。

- 【図2】図2は、本発明の実施の形態に係る半導体装置の基板を示す図である。

- 【図3】図3は、本発明の実施の形態で使用するテープキャリアを示す図である。

- 【図4】図4は、本発明の実施の形態に係る半導体装置の製造方法を説明する図である。

- 【図5】図5は、本発明の実施の形態に係る回路基板を示す図である。

- 【図6】図6は、本発明に係る方法を適用して製造された半導体装置を備える電子機器を示す図である。

### 【符号の説明】

- 1 半導体装置

- 10 半導体チップ

- 2 0 基板

- 2 2 配線

- 28 スルーホール

- 30 メッキ層

- 32 異方性導電材料

- 3 4 外部端子

- 40 キャリアテープ

- 42 配線パターン

- 50 回路基板

- 60 電子機器

## 【図1】

## 【図2】

# 【図3】

10

【図4】

【図6】

【図5】

## フロントページの続き

(56)参考文献 特開平11-330149(JP,A)

特開平11-297752(JP,A)

特開平11-176870(JP,A)

特開平08-330356(JP,A)

特開平11-214446(JP,A)

(58)調査した分野(Int.CI.<sup>7</sup>, DB名)

H01L 21/60 311

H01L 23/12