## A Distributed Computing Demonstration System Using FSOI Inter–Processor Communication

J. Ekman<sup>1</sup>, C. Berger<sup>2</sup>, F. Kiamilev<sup>1</sup>, X. Wang<sup>1</sup>, H. Spaanenburg<sup>3</sup>, P. Marchand<sup>4</sup>, S. Esener<sup>2</sup>

<sup>1</sup>University of Delaware, ECE Dept., Newark, DE 19716, USA <sup>2</sup>University of California San Diego, ECE Dept., La Jolla, CA 92093, USA <sup>3</sup>Mercury Computer Systems Inc., Chelmsford, MA 01824, USA <sup>4</sup>Optical Micro Machines, San Diego, CA 92121, USA

**Abstract.** Presented here is a computational system which uses free–space optical interconnect (FSOI) communication between processing elements to perform distributed calculations. Technologies utilized in the development of this system are integrated two–dimensional Vertical Cavity Surface Emitting Lasers (VCSELs) and MSM–photodetector arrays, custom CMOS ASICs, custom optics, wire–bonded chip–on–board assembly, and FPGA–based control. Emphasis will be placed on the system architecture, processing element features which facilitate the system integration, and the overall goals of this system.

## 1 Introduction

The area of optical interconnects is continually growing with many advances in optoelectronic devices, integration of CMOS ICs with these devices, and integration of hybrid electrical/optical devices into functional systems. It is clear that the flexibility in terms of scalability, and optical bandwidth which can be achieved by using optical interconnects will lead to changes in system architectures as designers move to to take advantage of this flexibility. As a part of the 3–D OptoElectronic Stacked Processor program[1], a demonstration system is being developed which illustrates the ability to construct distributed computational systems which use optical communication for passing data between processing elements. In this system, the distribution takes the form of linear chains of processors with nearest neighbor communication.

Communication between processors in a multiprocessor system quickly becomes the bottleneck and is therefore an ideal target for the integration of optical communication. One of the goals in developing this system was that of illustrating the use of optical communication in a low cost distributed system as a step toward validation of such architectures.

## 2 System Topology

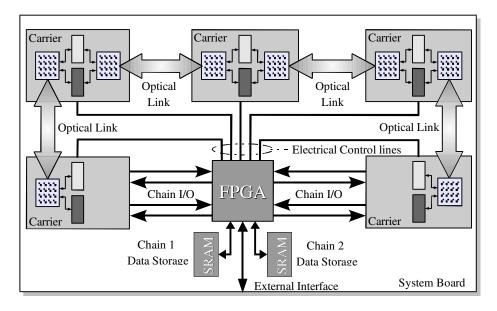

This demonstration system consists of two linear chains of five processors each. Three processors in each chain are configured to perform computation and the two remaining (one on each end of the chain) are configured to bring data into and out of each chain. This is accomplished by converting between electrical-domain (digital)

© Springer-Verlag Berlin Heidelberg 2000

and optical-domain (analog) signals at the ends of each chain (see figure 1). The two chains operate independently, but based on available optoelectronic device arrays, share OptoElectronic (OE) chips for communication. In addition to the ability to lengthen each chain, there is flexibility to scale the number of chains to yield a larger system. The optical chip-to-chip communication is achieved through the use of two dimensional VCSEL and MSM-photodetector arrays provided by Honeywell Technology Center[2] and custom optics designed at UCSD.

Figure 1. System diagram showing five carrier boards placed on system board. OptoElectronic arrays are shown on left and right sides of carrier boards and processing elements in the center of the carrier boards. The upper (*light*) PEs indicate one chain and the lower (*dark*) PEs indicate the second chain

## 2.1 Carrier Boards

Each unit in the chain is assembled onto a small "carrier board" where each of these carrier boards contains two processing elements (PEs) and two OE arrays. The OE arrays consist of sixteen VCSELs and sixteen photodetectors in an inter-digitated 4 x 4 array. These parts originally fabricated as a part of the GMU Co-Op program[3]. Each of the chips on the carrier boards are bare die, wire-bonded to contacts on the carrier board. One PE belongs to each of the two chains and the OE arrays are shared among the two chains with dedicated array elements for each chain. These carrier boards are then mounted onto a "system board" which also supports the optics, additional chips to provide control and system interface, and power connectors, etc. For the system described here, there are five carrier boards mounted onto one system board. This is illustrated in figure 1. Another goal of this demo system is to experiment with different opto-mechanics in an effort to