# Article A 14-Bit Hybrid Analog-to-Digital Converter for Infrared Focal Plane Array Digital Readout Integrated Circuit

Douming Hu, Libin Yao \*, Nan Chen, Jiqing Zhang, Shengyou Zhong, Wenbiao Mao, Fang Zhu and Juan Zhang

Kunming Institute of Physics, Kunming 650223, China \* Correspondence: libin\_yao@163.com

Abstract: This paper presents a 14-bit hybrid column-parallel compact analog-to-digital converter (ADC) for the application of digital infrared focal plane arrays (IRFPAs) with compromised power and speed performance. The proposed hybrid ADC works in two phases: in the first phase, a 7-bit successive approximation register (SAR) ADC performs coarse quantization; in the second phase, a 7-bit single-slope (SS) ADC performs fine quantization to complete the residue voltage conversion. In this work, the number of unit capacitors is reduced to 1/128th of that of a conventional 14-bit SAR ADC, which is beneficial for the application of small pixel-pitch IRFPAs. In this work, a tradeoff segmented thermometer-coded digital-to-analog converter (DAC) is adopted in the first 7-bit coarse quantization process: the lower 3-bit is binary coded, and the upper 4-bit is thermometer coded. A thermometer-coded DAC can improve the linearity of ADC. Capacitor array matching can be incredibly relaxed compared with a binary-weight 14-bit SAR ADC, resulting in a noncalibration feature. Moreover, by sharing DAC and comparator analog circuits between the SAR ADC and the SS ADC, the power consumption and layout area are consequently reduced. The proposed hybrid ADC was fabricated using a 180 nm CMOS process. The measurement results show that the proposed ADC has a differential nonlinearity of -0.61/+0.84 LSB and a sampling rate of 120 kS/s. The developed ADC achieves a temporal noise of 1.7 LSBrms at a temperature of 77 K. In addition, the SNDR is 72.9 dB, and the ENOB is 11.82 bit, respectively. Total power consumption is 71  $\mu$ W from supply voltages of 3.3 V (analog) and 1.8 V (digital).

Keywords: hybrid ADC; SAR ADC; SS ADC; infrared FPA; DROIC

# 1. Introduction

In recent years, there has been a trend in infrared imaging technology to reduce the pixel size, increase the resolution, decrease system costs, and enhance detector performance [1,2]. As infrared systems become increasingly compact, maintaining consistent system performance has emerged as a critical objective. One of the primary strategies to achieve this is to decrease the pixel pitch of the infrared detector while simultaneously enhancing performance through technological advancements [3-6].

With classical analog outputs, high pixel rates lead to increases in both the number of analog video outputs and the overall detector power consumption. Moreover, the analog detector SNR can be degraded by the required external analog acquisition chain operating at ambient temperature. The noise of external ADCs is comparable with the readout integrated circuit (ROIC) output noise, which degrades the overall SNR. Developing onchip, high-performance, ultra-low-power analog-to-digital converters (ADCs) has thus become a crucial trend to meet system requirements. The ADC of digital readout integrated circuits (DROICs) is critical to the infrared detector performance.

In [7–9], small-pixel digital sensors provide advantages in reducing the size, weight, and power (SWaP), improving noise immunity, simplifying interfacing requirements, and lessening susceptibility to electromagnetic interference (EMI). DROIC, which is based on

Citation: Hu, D.; Yao, L.; Chen, N.; Zhang, J.; Zhong, S.; Mao, W.; Zhu, F.; Zhang, J. A 14-Bit Hybrid Analog-to-Digital Converter for Infrared Focal Plane Array Digital Readout Integrated Circuit. Sensors 2024, 24, 3653. https://doi.org/10.3390/ s24113653

Received: 9 May 2024 Revised: 31 May 2024 Accepted: 3 June 2024 Published: 5 June 2024

Copyright: © 2024 by the authors. Licensee MDPI, Basel, Switzerland, This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/).

pixel-level ADC, directly accomplishes analog-to-digital conversion in a pixel array [10–13]. However, this form of pixel-level ADC is only suited for usage in large-sized pixels.

In small-pixel infrared sensors, column-level digital readout circuits are more common due to spatial constraints since the ADC area is limited to a one-dimensional direction.

The single-slope (SS) ADC is the most widely employed in CMOS Image Sensor (CIS) applications because it can be implemented in a narrow column pitch using simple column circuits consisting of a comparator and a counter [14,15]. However, a major drawback of SS ADCs is their relatively slow conversion speed. Each K-bit A/D conversion requires 2<sup>K</sup> clock periods compared to only K clock periods for successive approximation register (SAR) ADCs and cyclic ADCs. In high-resolution designs, their slow conversion efficiency significantly limits the readout speed of the array. Due to the high dynamic range of infrared images, DROICs typically require high-resolution ADCs above 14 bits. The conversion speed of a conventional pure 14-bit SS ADC is limited by the counting frequency, resulting in high power consumption. SAR ADCs offer a significant advantage in conversion speed; a 14-bit SAR ADC only requires 14 clock periods for conversion. However, SAR ADCs need calibration in high-resolution designs (e.g., greater than 12 bits). Calibration helps save substantial power in the DAC and comparator by correcting their errors, but the calibration overhead in terms of the area, speed, power, and architectural complexity should be minimized [16]. Furthermore, a 14-bit SAR ADC requires  $2^{14}$  unit capacitors, which consume a larger chip area. When the IRFPA pixel pitch is less than 10 μm, designing and laying out a 14-bit column-parallel SAR ADC becomes a considerable challenge, limiting its application in small pixel pitch IRFPAs.

To overcome the limitations of both SS and SAR ADCs, hybrid and two-step ADCs have been developed [17–22]. These include multiple-ramp single-slope (MRSS) ADCs [18] and two-step single-slope (TSSS) ADCs [19,20], which aim to balance the advantages of both approaches. For example, an 11-bit two-step ADC [19] combining a 3-bit SS ADC and an 8-bit SAR ADC can ease capacitor array matching requirements without the need for calibration. A 12-bit TSSS ADC [22] with a constant input-common-mode level resistor ramp employs a current-mode R-2R DAC and a feedback R-string DAC to enhance ADC linearity, but it still requires a redundancy of 1.5 bits. Nonetheless, implementing such designs above a 14-bit resolution remains challenging due to circuit complexity and area constraints. The SAR/SS ADC [21] approach reduces the capacitor area and power consumption by sharing analog circuits and minimizing calibration needs. Despite these advancements, achieving high resolution and low power consumption within narrow readout channel pitches remains complex.

Because infrared images have a high dynamic range, the resolution of an ADC in a DROIC is usually larger than 14 bit. High-resolution ADCs require longer conversion times and higher power consumption. Therefore, for the infrared system DROIC, an ADC with low power consumption, a high speed, and a high resolution is urgently needed. To address these issues, power-efficient and area-efficient ADCs for the digital readout integrated circuit (DROIC) are proposed in this work.

The proposed ADC can be implemented in 10  $\mu$ m small pixel pitch IRFPAs. It is suitable for a column-parallel ADC of a digital readout integrated circuit for IRFPAs. With the sampling frequency of 120 kSps and low power consumption, differential nonlinearity |DNL| < 1, the proposed ADC is attractive for high-frame-rate digital infrared sensors.

The remainder of this article discusses the architecture, operating principles, and implementation details of this proposed ADC, providing measurement results and comparing them with previous works to highlight its advantages and improvements.

## 2. Architecture of the Proposed ADC

## 2.1. Block Diagram

With the combination of the SAR and SS architecture, the suggested hybrid SAR-SS ADC can achieve both the high linearity of the SS ADC and the high sampling rate of the SAR ADC, which makes it appropriate for IRFPA. This integration retains the individual

benefits of each type of ADC while mitigating their drawbacks. A coarse SAR ADC and fine SS ADC share a capacitor DAC, ensuring there is no gain error between the coarse and fine quantization stages.

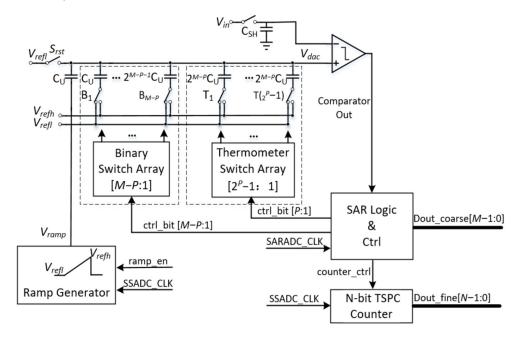

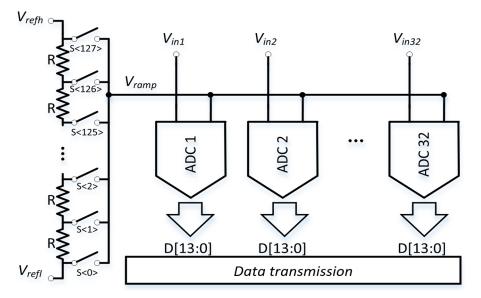

Figure 1 shows a block diagram for the proposed two-step column-parallel ADC. The system consists of an N-bit counter, global ramp generator, SAR logic and control circuits, comparator, sample-and-hold circuits, binary switch array, thermometer code switch array, and  $2^{M} C_{U}$  capacitor DAC. The SAR ADC first conducts coarse M-bit quantization, followed by fine N-bit quantization by the SS ADC, resulting in a combined (M + N) bit quantization.  $V_{refl}$  and  $V_{refh}$  are the reference voltages for the capacitor DAC and ramp generator, respectively. The ramp generating block provides the ramp signal, Vramp. To eliminate linearity errors caused by variations in the ramp signal and the capacitor DAC's gain error, the ramp signal Vramp is connected to the bottom plate of  $C_{U}$  in the capacitor DAC [21]. For every column, the comparator is shared by SAR ADC and SS ADC. Additionally, a global ramp generator is shared by all columns. For each column, the comparator is shared by all columns.

Figure 1. A block diagram of the proposed hybrid ADC and global ramp generator.

While the binary weighted successive approximation register (SAR) is energy efficient, it is susceptible to errors caused by digital-to-analog converter (DAC) settling and mismatches in DAC capacitors [23]. In contrast, a thermometer code offers several advantages over a binary code, including natural monotonicity, no missing codes, and superior DNL performance. The proposed segmented thermometer-coded capacitor DAC is split into upper P-bit and lower (M-P) bits for use in M-bit coarse SAR quantization, as seen in Figure 1. The upper P-bit section of the capacitor DAC is controlled by a thermometer switch array, while the remaining lower (M-P) bit section maintains a binary switch. This segmented approach allows the higher bits to provide better linearity compared to a purely binary-weighted DAC. By ensuring monotonic features and avoiding glitches caused by voltage peaks, the segmented thermometer-coded DAC can reduce DNL while maintaining the same capacitor area [24]. For instance, an M-bit thermometer-coded decoder would have a  $2^{M} - 1$  control signal since these require greater space. Given the challenges of implementing a thermometer code decoder in a compact pixel readout channel, this study presents the highest P-bit segment as a feasible solution. In summary, the segmented thermometer-coded DAC improves linearity and reduces DNL, making it a better fit for applications requiring high precision and reliability.

#### 2.2. The Operating Principle of the Proposed Hybrid ADC

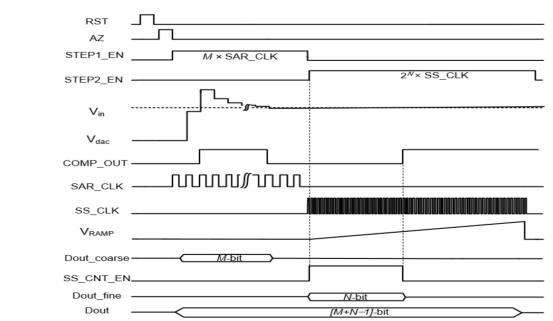

Figure 2 depicts a simplified operational timing diagram. In the first phase, coarse quantization is performed by the M-bit SAR ADC, which only requires M clock cycles, making the coarse conversion speed very fast. At each rising edge of the SAR clock, the comparator compares the output of the capacitor DAC  $V_{dac}$  to  $V_{in}$ . Based on the comparator's output, the SAR logic selects either the  $V_{refl}$  or  $V_{refh}$  reference voltages to connect to the bottom plate of each capacitor in the DAC. Once the M-bit SAR ADC completes coarse quantization, the residue voltage,  $V_{res}$ , can be expressed as follows:

$$V_{res} = V_{in} - \sum_{i=0}^{M-1} \left[ \frac{\left( V_{refh} - V_{vrefl} \right)}{2^{M-i}} \cdot Dout\_coarse[i] \right] - V_{vrefl}$$

(1)

where Dout\_corase[i] represents the i-th bit of the upper M-bit. In the second step, the N-bit SS ADC performs fine quantization to complete the residue voltage conversion. The ramp-generated block produces a ramp signal,  $V_{ramp}$ , which is connected to the bottom plate of the least significant bit  $C_U$  in the DAC. During SS ADC quantization,  $V_{ramp}$  varies from  $V_{refl}$  to  $V_{refh}$ , consisting of a total of  $2^N$  steps with a step size of  $(V_{refh} - V_{refl})/(2^N - 1)$ , and the  $V_{dac}$  can be represented as follows:

$$V_{dac} = \sum_{i=0}^{M-1} \left[ \frac{\left( V_{refh} - V_{vrefl} \right)}{2^{M-i}} \cdot Dout\_coarse[i] \right] + V_{vrefl} + \sum_{j=0}^{N-1} \left[ \frac{\left( V_{refh} - V_{vrefl} \right)}{2^{(M+N-j)}} \cdot Dout\_fine[j] \right]$$

(2)

Figure 2. Operational timing diagram of proposed ADC.

Once the comparator output is triggered, the SS ADC stops counting. As a result, the ultimate outcome of the two-step conversion is obtained, and the (M + N) bit output D can be stated as

$$\mathbf{D} = \left\{ Dout_{coarse[M-1]}, \dots, Dout_{coarse[0]}, Dout_{fine[N-1]}, \dots, Dout_{fine[0]} \right\}$$

(3)

The conversion time of the proposed ADC can be briefly expressed as follows:

$$TIME_{conversion} = M \times SAR\_CLK + 2^N \times SS\_CLK \tag{4}$$

#### 3. The Design of the Proposed Hybrid ADC

# 3.1. The Trade-off between the SAR and SS ADC

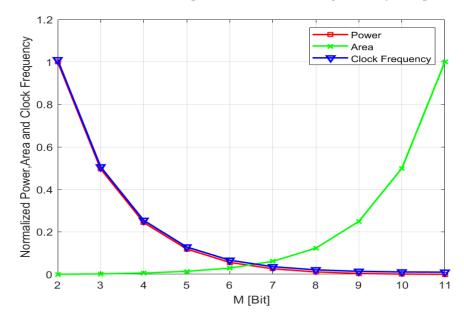

In the proposed 14-bit hybrid ADC, M represents the number of bits in the SAR ADC, while the SS ADC handles the remaining (14-M) bits. Choosing the value of M is crucial. As illustrated in Figure 3, for a 14-bit ADC with a constant sampling rate, increasing M reduces N, which, in turn, lowers the clock frequency and power consumption of the SS ADC. Nonetheless, the area of the capacitor arrays grows exponentially with the M value. When M exceeds 8 bits, the capacitor area increases significantly, complicating the layout.

Figure 3. A plot of the power, area, and clock frequency as a function of the M-bit in the first step.

Since the ADC needs to fit within narrow pitch applications, using an SAR ADC with fewer than 8 bits is more area efficient. As shown in Figure 3, the ADC achieves good power efficiency for both M = 6 and M = 7. Compared to M = 6 and N = 8, where the fine SS ADC takes  $2^8$  clock cycles, M = 7 and N = 7 only require 27 clock cycles, giving the M = 7 and N = 7 configurations a speed advantage. Therefore, setting M = 7 and N = 7 is a good compromise, balancing the layout size, power consumption, and conversion speed. This is why this work uses a 7-bit SAR ADC and a 7-bit SS ADC.

The thermometer-coded DAC offers the advantage of having a less strict matching requirement compared to a binary-weighted DAC. A 50% matching of the unit cell is sufficient to achieve a DNL of 0.5 LSB [23]. This allows for good DNL performance within the same area using a thermometer-coded DAC. The image system requirements for INL are generally less stringent compared to those for DNL. For IRFPA applications, ensuring good DNL performance is crucial. However, a significant disadvantage of a thermometer-coded DAC is its increased area. If the number of bits exceeds 4, the thermometer code switch array becomes complex and difficult to implement within a small IRFPA readout channel.

Typically, segmentation is used to strike a balance between the clear advantages of the thermometer-coded architecture and the need to keep the area limited. In this study, a segmented capacitor DAC is introduced. The DAC is divided into two sub-DACs: one for the upper bits and one for the lower bits. For the higher bit, where accuracy is the most crucial, thermometer coding is employed. For instance, a 4-bit binary to thermometer decoder uses 15 control signals for the capacitor switch, which can be implemented in a small channel. However, if a 5-bit de-coder is chosen, the number of control signals increases to 31, making the layout in the ADC channel more challenging. For the 7-bit DAC, using the higher 4 bits with thermometer coding in the 10  $\mu$ m pitch is a good compromise to balance the circuit area and DNL performance. Therefore, the lower 3 bits use a binary-code DAC, while the upper 4 bits use a thermometer-code DAC. This setup allows the 7-bit SAR

ADC to perform coarse quantization in the first phase with only 7 SAR clock cycles. In the second phase, a 7-bit SS ADC conducts fine quantization using 2<sup>7</sup> SS clock cycles.

The value of the unit capacitor, Cu, is a compromise considering thermal noise, the process capacitance error, parasitic capacitance, and the switching mode of the capacitor array. A higher Cu value improves noise and the matching performance, whereas a lower value is better for power consumption, the chip area, and the settling speed. According to the process parameter of the metal–insulator–metal (MIM) capacitor and Monte Carlo simulation, the matching requirement of the capacitor array can be met with a unit capacitance of 79 fF. Due to spatial limitations and KT/C noise, an MOS capacitor with a capacitance of 2.1 pF has been selected for the sample and hold capacitor.

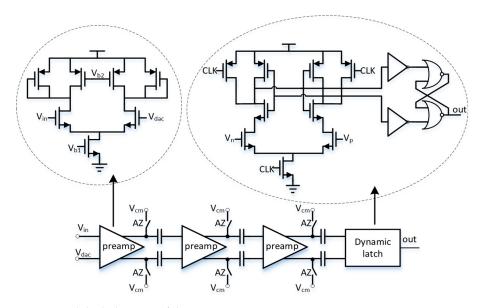

#### 3.2. Comparator

A fast and high-precision comparator is essential for high-resolution ADCs. Regenerative comparators with several-stage amplifiers are widely used in pure SAR ADCs [23,25]. Figure 4 shows a simplified diagram of the comparator used in the proposed hybrid ADC. The comparator consists of three-stage amplifiers, a regenerative dynamic latch, and autozeroing capacitors. In this study, a three-stage pre-amplifier construction is employed to enhance the open-loop gain for the hybrid ADC application. The pre-amplifier uses a differential amplifier with a current-starved load, providing an easy way to balance bandwidth and gain. Moreover, the comparator's clock can be regulated using the SAR and SS clocks during the first and second steps, respectively. An auto-zeroing mechanism is also included, which activates at the beginning of the comparison process.

Figure 4. A b lock diagram of the comparator.

In this design, the comparator is shared by both the SAR ADC and the SS ADC. During the coarse SAR ADC phase, the residual signal decreases as a result of the SAR bit cycling. A regenerative comparator makes the comparison by sensing a minimal static residue voltage in the LSB bit cycle. Sensing and amplifying a smaller residue signal helps extend the decision time needed to determine logical level "1" or "0". A metastable state occurs if the decision delay is longer than a limited comparison time, which is critical in high-speed SAR ADCs [26]. There is only one comparison required by the SS ADC in the fine SS ADC phase. High-speed, high-precision comparators for SAR logic typically require more current for the amplifiers, leading to significant power consumption. Therefore, the comparator's power consumption can be efficiently reduced by appropriately relaxing the SAR ADC's clock frequency. To address this, the period of the SAR clock is set to be

four times longer than that of the SS clock. Thus, Equation (4) can be represented by the conversion time as follows:

$$TIME_{conversion} = 7 \times 4 \times SS\_CLK + 2^{7} \times SS\_CLK$$

(5)

In this work, the SAR ADC operates at a frequency of 12.5 MHz, while the SS ADC clock's frequency is 50 MHz. This setup strikes an excellent balance between power consumption and speed, ensuring the linearity of the 7-bit MSB quantization and enhancing the DNL.

The noise from the first-stage pre-amplifier comparator is the primary noise source, so it is crucial to have a relatively high bias current for this stage. The first stage has a quiescent current of 6  $\mu$ A, while the subsequent stages each have a quiescent current of just 3  $\mu$ A. To minimize the response delay of the comparator, the 3 dB bandwidth is set to around 100 MHz.

The dynamic comparator has the advantages of low power consumption, a short transmission delay, and a low input offset voltage. It only consumes dynamic power during clock edges, making it highly energy efficient [26]. The dynamic latch performs the timing comparison and generates a digital output based on which input signal becomes high first without consuming any static power. However, the dynamic latch can introduce significant kickback noise, negatively impacting ADC performance [27,28]. To address this, the comparator offsets are cancelled at the start of the conversion process using the auto-zeroing function. This effectively reduces the influence of DC offset voltage in both the latch and the pre-amplifier, improving the overall ADC performance.

# 3.3. Ramp

As shown in Figure 5, the global ramp generator is shared by all column ADCs in the DROIC IRFPAs. In this multiple-project wafer (MPW), there are 32 ADCs in the array. After the conversion, all of the ADC data are transmitted by the transmission module.

**Figure 5.** A block diagram of the global ramp generator and proposed column-parallel ADCs in IRFPAs.

In the second step of the proposed ADC, the ramp is generated by a 7-bit resistor-string DAC (RDAC). For each step of the RDAC,  $V_{STEP} = (V_{refh} - V_{refl})/127$ . The settling time of each RDAC step is given by the following equation:

$$\Delta V_{RAMP}(t) = \left(1 - e^{-t/\tau}\right) * V_{STEP} \tag{6}$$

where  $\tau = R_{driver} \times C_{load}$ , and  $R_{driver} \approx R1 + R_{load}$ . R1 = 1/2(127 \* R) in the worst case.  $R_{load}$  refers to the metal resistor value of the ramp layout. The total capacitive load of the ramp includes  $C_{lumped}$ , which represents the parasitic capacitance of the layout, as well as the load capacitance of 32 ADC's C<sub>U</sub> array.

$$C_{LOAD} \approx \left( C_{lumped} + 32 \times C_U \right)$$

(7)

The RDAC is frequently used due to its simple structure and inherent monotonicity. The theoretical values of the 7-bit RDAC INL is given by  $0.5\sqrt{2^7 - 1}\sigma$ , where the factor 0.5 comes from the fact that the INL curve was fit to zero at both ends of the curve [24]. Resistors  $\sigma$  is a function of area,  $\sigma^2 \propto 1/area$ . The INL requirements for the ADC are more relaxed in the case of image sensors because the pixels contribute more to the nonlinearity of the system. Therefore, the impact of the resistor-string DAC INL on the whole ADC can be neglected.

The ramp generator consists of a resistor string comprising 127-unit resistors, R, each with a resistance of 50  $\Omega$ . With the ADC's sampling rate being 120 kS/s, the SS ADC clock frequency during the fine 7-bit conversion is 50 MHz. This means VRAMP spends 20 ns for each RDAC step. The proposed ADC can quantify the input signal between V<sub>refl</sub> and V<sub>refh</sub>, which are set to 1.2 V and 3.1 V, respectively. The analog circuitry is powered by 3.3 V, while the digital circuits operate at 1.8 V.

#### 3.4. Layout

The number of unit capacitors of the proposed two-step ADC is reduced to 1/128th of that in a conventional 14-bit SAR ADC, making it very area-efficient. The proposed two-step ADC is low in area occupancy, and the layout can be implemented in a pixel pitch of less than 10  $\mu$ m. This design allows the layout to fit within a pixel pitch of less than 10  $\mu$ m.

Since the DNL is more sensitive to the capacitor mismatch than the resistive mismatch, the proposed hybrid ADC requires the capacitor DAC to have a careful layout to ensure the accurate conversion of the upper 7 bits. To address this, dummy capacitors are placed on both sides of the 7-bit DAC to minimize capacitance mismatch. Another factor to consider is the effect of oxide thickness gradients over large capacitor areas. As discussed in previous studies [29], arranging capacitors around a common centroid helps minimize the impact of long-range gradients in oxide thickness. Additionally, dummy resistors are placed on both sides of the 7-bit RDAC to reduce resistor mismatch. This careful attention to layout details helps ensure the proposed ADC achieves high performance and accuracy.

# 4. Measurement Results and Discussion

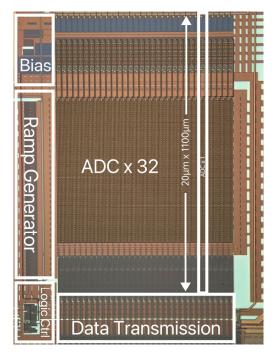

The proposed hybrid ADC arrays are fabricated in a 180 nm 1P6M CMOS process. The chip comprises 32 ADCs, an RDAC ramp generator, bias circuits, logic ctrl circuits, and data transmission circuits. The hybrid ADC occupies 20  $\mu$ m  $\times$  1100  $\mu$ m, as shown in Figure 6.

#### 4.1. Measurement Setup

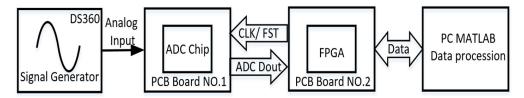

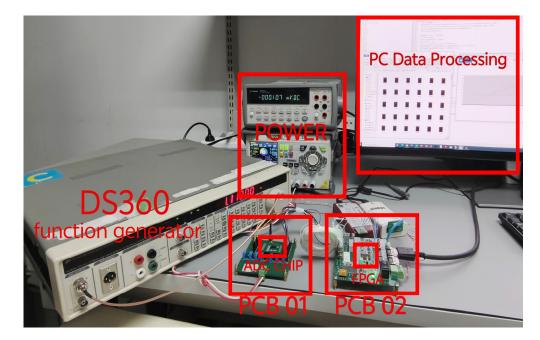

Figure 7 shows a block diagram of the measurement setup, and Figure 8 presents an image of the test measurement setup. Figure 9 illustrates the ADC chip mounted on the board along with our custom-designed PCB for ADC testing. The input signal from the DS360 waveform generator is fed to the PCB through an SMA connector. A customized power board labeled as No.1 provides the necessary power supply and reference voltages for both the analog and digital parts, and it drives the on-chip voltage buffers. An FPGA on board No.2 generates the clock and FST signals, and it captures the digital output data stream from the ADC output. These data streams are then exported to MATLAB for processing and computing the Fast Fourier Transform (FFT).

Figure 6. A microscope photo of the proposed ADC chip.

Figure 7. Block diagram of measurement setup.

Figure 8. Measurement setup.

Figure 9. An image of the ADC chip and the custom-designed PCB for testing.

#### 4.2. Measurement Results

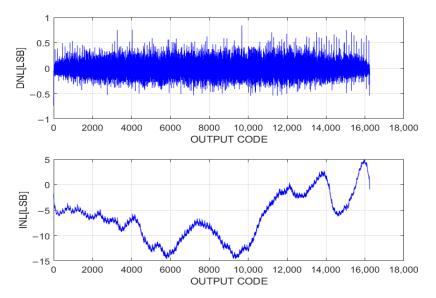

At a 120 kS/s sampling rate, the measured DNL and INL of the proposed ADC are plotted in Figure 10. The measured DNL is -0.61 to +0.84 LSB without calibration, staying within  $\pm 1$  LSB across the entire output range at a 14-bit resolution. In this design, a mismatch in the binary ratios of capacitors in the array and the kick-back noise from the comparator contribute to the DNL and INL errors. Since the single-ended method, as shown in Figure 1, the difference can be up to one-quarter of the supply voltage. It might cause a gain or INL error due to the comparator's insufficient common-mode rejection ratio (CMRR) [30]. The peak-to-peak value of the INL is -14.5 to +4.8 LSB. However, for image sensor applications, INL errors have a negligible impact on photo quality [31–33].

Figure 10. DNL and INL of proposed hybrid ADC.

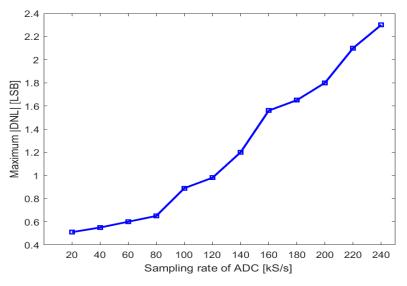

In order to explore the influence of a higher sampling rate on the ADC, the DNL of the ADC at a higher sampling rate is tested. The curve in Figure 11 plots the maximum |DNL| as a function of the sampling rate. When the sampling frequency exceeds 120 kS/s, the maximum |DNL| value rises above 1. This increase in DNL errors is primarily due

to the limited speed of the comparator. The proposed ADC achieves its best linearity and optimal FoM2 at the sampling rate of 120 kS/s.

Figure 11. A plot of the maximum | DNL | as a function of the sampling rate.

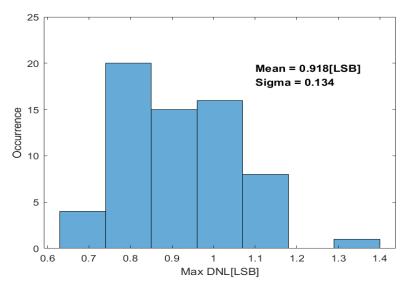

A total of 64 ADC samples were tested, and the measurement results for the maximum |DNL| are presented in the histogram in Figure 12. The mean value of the maximum |DNL| is 0.918 LSB.

Figure 12. Measured maximum | DNL | of 64 ADC test samples.

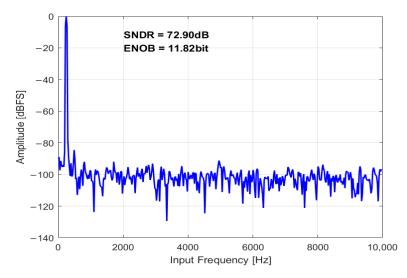

To test the dynamic characteristics of the proposed ADC, a sinusoidal signal with a frequency of 344 Hz and  $V_{peak-to-peak}$  of 1.9 V is used as the input signal. Figure 13 shows the result of the 4096 points' Fast Fourier Transformation (FFT). With a sampling rate of 120 kS/s, the ADC achieves a measured signal-to-noise and distortion ratio (SNDR) of 72.9 dB, corresponding to an effective number of bits (ENOB) of 11.82 bit. At a 14-bit resolution, 1 LSB corresponds to 115.9  $\mu$ V with 1.9 V<sub>FS</sub>. At room temperature, the average value of the temporal noises is 2.5 LSB rms. At the liquid nitrogen temperature of 77 K for a cooled IRFPAS, the proposed ADC achieves a lower temporal noise of 1.7 LSB rms than at room temperature.

Figure 13. Measured FFT plot of proposed ADC.

The analog circuits are powered by a 3.3 V supply, and the digital circuits are powered by a 1.8 V supply. At a sampling rate of 120 kS/s, the total power consumption of each proposed ADC is 71  $\mu$ W. The power distribution is as follows: 40  $\mu$ W for the comparator, 21  $\mu$ W for the SAR logic and thermometer decoder, and 10  $\mu$ W for the counter.

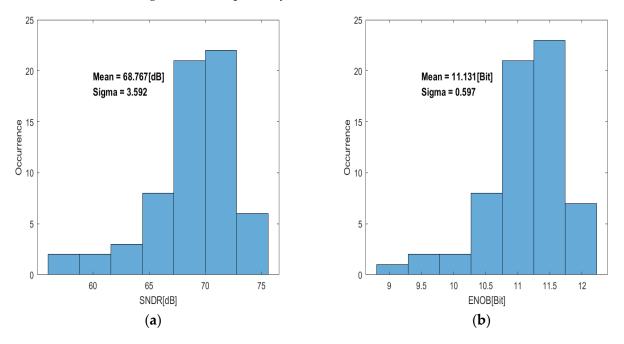

The histograms for the SNDR and ENOB of the 64 ADC samples are shown in Figure 14a,b, respectively. The mean SNDR is 68.76 dB, and the mean ENOB is 11.13 bits.

Figure 14. Measured dynamic performance of 64 ADC samples: (a) SNDR and (b) ENOB.

Table 1 summarizes the measured performance and compares it with earlier ADCs of similar architectures.

The figure of merits 1 (FoM1) is obtained from an equation in [21], and the FoM2 is obtained according to the Walden FoM equation [28]. These figures of merit are calculated to compare the power efficiency of the ADCs. Additionally, the Schreier figure of merit (FoMS) is calculated for a fair comparison across different resolutions. Since the comparator's pre-amplifier uses a high supply voltage of 3.3 V, the power dissipation in this work is not the lowest. Consequently, it achieved a Walden FoM2 of 196.3 fJ/conv and a Schreier FoM<sub>S</sub> of 162 dB. The proposed ADC also demonstrates high area efficiency with 6.08  $\mu$ m<sup>2</sup>/code,

making it suitable for small-pixel IRFPA applications. Furthermore, it achieved a good |DNL| < 1 without calibration at a sampling rate of 120 kS/s. However, due to mismatches and parasitic capacitance, the binary-weighted characteristics are not perfectly maintained. If the proposed ADC was to include comparator offset calibration techniques and error correction circuits, the ENOB and INL could be further improved, albeit at the cost of additional calibration circuitry.

[21] [22] [20] [23] [34] This Work **TED 2016 VLSI 2022** Sensor J 2020 **ISCAS 2020** Electron 2022 Process 90 nm 130 nm 180 nm 180 nm 28 nm 180 nm Supply voltage (V) 2.8/1.23.3/1.22.8/1.51.8 N/A 3.3/1.8Architecture SAR/SS TS SS TS SS SAR/SS SAR/SS SAR/SS Resolution (bit) 12 12 14 14 12 10 11.82 ENOB (bit) N/A 9.8 9.13 9.1 10.81 2.7 10 0.8 Conversion time (µs) 39.7 2.8 8.3 56 6.53 36 34 71 Power  $(\mu W)$ 62 DNL (LSB) -0.45/+0.84-1/+0.83-1/+4.25-0.61/+0.6-1/+2.5-0.61/+0.84INL (LSB) -1.5/+0.74-3.31/+4.78-7.3/+5.73 -0.89/+0.82-3.3/+3.6-14.5/+4.8\* FoM1 (fJ/conv) 43.3 36.9 151.3 1.75 87.89 5.8 \*\* FoM2 (fJ/conv) N/A 695.5 447 52.5 53 196.3 \*\*\* FoM<sub>S</sub> (dB) N/A 149.6 149.4 158.8 163.8 162 Area(µm<sup>2</sup>)  $2.24 \times 998$  $7.5 \times 675$  $5.6 \times 1007$  $60 \times 200$  $550 \times 1180$  $20 \times 1100$ \*\*\*\* AE(µm<sup>2</sup>/code) N/A 5.68 10.6 21.8 361 6.08

Table 1. Performance comparison with previous works.

\* FoM1 = [ Power]/( $[1/f_s] \times 2^{[Resolution]}$ ). \*\* FoM2 = [Power]/( $[1/f_s] \times 2^{[ENOB]}$ ). \*\*\* FoM<sub>S</sub> = SNDR (dB) + 10log(Bandwidth/[Power]) = (6ENOB + 1.8) (dB) + 10log(Fs/2/[power]). \*\*\*\* AE = [ Area]/(2^{[ENOB]}).

#### 5. Conclusions

This paper presents a 14-bit hybrid column-parallel ADC for small pixel pitch IRFPA applications. This hybrid ADC combines a 7-bit coarse SAR ADC with a 7-bit fine SS ADC, achieving a good balance between speed and power consumption. Only using a capacitor array for the 7-bit resolution to achieve a 14-bit ADC is a well-suited method for IRFPAs with small pixel pitches. Moreover, a tradeoff segmented thermometer-coded DAC is adopted in the first 7-bit coarse quantization, improving linearity and reducing the complexity of capacitor array matching.

A prototype chip with 32 ADCs was fabricated in a 0.18  $\mu$ m process. A total of 64 ADC samples were tested. The ADC consumes 71  $\mu$ W at a sampling rate of 120 kS/s, achieving an FoM<sub>W</sub> of 196.3 fJ/conv and an FoM<sub>S</sub> of 162 dB. Thanks to the segmented thermometer DAC, the proposed hybrid ADC achieves a differential nonlinearity of -0.48/+0.94 LSB without calibration or redundancy bits. The proposed ADC is suitable for small pixel pitch IRFPA readout applications. It has a high resolution and is power-efficient and area-efficient, making it suitable for digital readout integrated circuits for SWaP-constrained applications.

Author Contributions: Conceptualization, D.H. and L.Y.; Data Curation, D.H.; Formal Analysis, J.Z. (Jiqing Zhang), S.Z. and W.M.; Funding Acquisition, N.C.; Investigation, D.H. and L.Y.; Methodology, D.H. and L.Y.; Project Administration, N.C. and J.Z. (Jiqing Zhang).; Software, D.H. and F.Z.; Writing—Original Draft, D.H.; Writing—Review and Editing, D.H., N.C., J.Z. (Jiqing Zhang), S.Z., W.M. and J.Z. (Juan Zhang). All authors have read and agreed to the published version of the manuscript.

Funding: This research was funded by the Yunnan Province Innovation Team Project (202305AS350026).

Institutional Review Board Statement: Not applicable.

Informed Consent Statement: Not applicable.

Data Availability Statement: Data are contained within the article.

Conflicts of Interest: The authors declare no conflicts of interest.

## References

- Reibel, Y.; Pere-Laperne, N.; Augey, T.; Rubaldo, L.; Decaens, G.; Bourqui, M.L.; Manissadjian, A.; Billon-Lanfrey, D.; Bisotto, S.; Gravrand, O.; et al. Getting Small, new 10 μm pixel pitch cooled infrared products. *Infrared Technol. Appl. XL* 2014, 9070, 886–895. [CrossRef]

- Hood, A.D.; Huang, E.K.; Yang, K.; Hibberd, D.; Loung, V.; Oleson, M.; Lott, R.; Pratt, C.; Thomas, J.; Costolo, M.; et al. Small pixel pitch, high-definition MWIR, and dual band SWIR/MWIR imaging sensors for SWaP-constrained applications. *Infrared Technol. Appl. XLIX* 2023, 12534, 140–148. [CrossRef]

- 3. Billon-Lanfrey, D.; Trinolet, P.; Pistone, F.; Rubaldo, L.; Huet, H. New IR detectors with small pixel pitch and high operating temperature. *Infrared Millim. Wave Terahertz Technol.* **2010**, *7854*, 128–138. [CrossRef]

- Reibel, Y.; Péré-Laperne, N.; Rubaldo, L.; Augey, T.; Decaens, G.; Badet, V.; Badet, V.; Baud, L.; Roumegoux, J.; Kessler, A.; et al. Update on 10µm pixel pitch MCT-based focal plane array with enhanced functionalities. *Infrared Technol. Appl. XLI* 2015, 9451, 639–653. [CrossRef]

- Caulfield, J.T.; Curzan, J.P.; Norton, A.; Terterian, S.; Sharifi, H. Small pixel HD MWIR camera technology. *Infrared Technol. Appl.* XLVIII 2022, 12107, 443–449. [CrossRef]

- Poonnen, T.; McCotter, S.; Esparza, K.; Veeder, K. Digital readout integrated circuit for high dynamic range infrared imaging. *Infrared Technol. Appl. XLIX* 2021, 11740, 29–33. [CrossRef]

- Baier, N.; Gravrand, O.; Le Goff, T.; Lobre, C.; Rabaud, W.; Rochette, F.; Brunner, A.; Grezes, C.; Morisset, N.; Rubaldo, L. Small pixel pitch MCT P on N MWIR photodiodes at DEFIR: Towards 7.5um and beyond with very high image quality. *Infrared Technol. Appl. XLIX* 2023, 12534, 246–254. [CrossRef]

- 8. Caulfield, J.T.; Curzan, J.P.; Sharifi, H.; Terterian, S.; Veeder, K.; Dhawan, N. High-definition and ultra-high-definition IR camera technology. *Infrared Technol. Appl. XLIX* **2023**, 12534, 205–212. [CrossRef]

- Huang, E.; Thomas, J.; Hibberd, D.; Luong, V.; Lott, R.; Oleson, M.; Hood, A.; MacDougal, M.H. Small pixel MWIR sensors for low SWaP applications. *Infrared Technol. Appl. XLVII* 2021, 11741, 123–129. [CrossRef]

- 10. Zeng, Y.; Yang, S.; Liu, Y.; Bao, R.; Zhu, Z.; Lin, J.; Zhou, X.; Chen, Y.; Yin, J.; Mak, P.I. A Digital Readout Integrated Circuit Based on Pixel-level ADC Incorporating On-chip Image Algorithm Calibration for IRFPA. *IEEE Sens. J.* 2023, 23, 21747–21756. [CrossRef]

- 11. Abbasi, S.; Ceylan, O.; Gurbuz, Y. A DROIC based on PFM ADCs employing over-integration for error shaping. *IEEE Trans. Circuits Syst. I Regul. Papers* 2019, *66*, 3713–3722. [CrossRef]

- Zeng, Y.; Yang, S.; Liu, Y.; Li, Z.; Huang, W.; Huang, X.; Zhou, X.; Liu, J.; Li, Q. A 640× 512 30µm Pixel Pitch 1.8 mK-NETD 90.1 dB-SNR Digital Read-out Integrated Circuit with Fully on-Chip Image Algorithm Pixel-Level Calibration. In Proceedings of the 2021 IEEE Asian Solid-State Circuits Conference (A-SSCC), Busan, Republic of Korea, 7–10 November 2021; pp. 1–3. [CrossRef]

- Lu, H.; Zhou, Y.; Lu, W.; Zhang, Y.; Chen, Z. High Frame Rate High Precision ROIC with Pixel-Level CCO-Based ADC for Infrared FPAs. In Proceedings of the 2023 IEEE 15th International Conference on ASIC (ASICON), Nanjing, China, 24–27 October 2023; pp. 1–4. [CrossRef]

- 14. Nie, K.; Zha, W.; Shi, X.; Li, J.; Xu, J.; Ma, J. A single slope ADC with row-wise noise reduction technique for CMOS image sensor. *IEEE Trans. Circuits Syst. I Regul. Pap.* **2020**, *67*, 2873–2882. [CrossRef]

- 15. Kim, H.J. 11-bit column-parallel single-slope ADC with first-step half-reference ramping scheme for high-speed CMOS image sensors. *IEEE J. Solid-State Circuits* **2021**, *56*, 2132–2141. [CrossRef]

- 16. Ding, M.; Harpe, P.; Liu, Y.H.; Busze, B.; Philips, K.; De Groot, H. A 46 μW 13 b 6.4 MS/s SAR ADC with background mismatch and offset calibration. *IEEE J. Solid-State Circuits* **2016**, *52*, 423–432. [CrossRef]

- 17. Lim, S.; Lee, J.; Kim, D.; Han, G. A high-speed CMOS image sensor with column-parallel two-step single-slope ADCs. *IEEE Trans. Electron Devices* **2009**, *56*, 393–398. [CrossRef]

- 18. Snoeij, M.F.; Theuwissen, A.J.; Makinwa, K.A.; Huijsing, J.H. Multiple-ramp column-parallel ADC architectures for CMOS image sensors. *IEEE J. Solid-State Circuits* 2007, 42, 2968–2977. [CrossRef]

- 19. Tang, F.; Chen, D.G.; Wang, B.; Bermak, A. Low-power CMOS image sensor based on column-parallel single-slope/SAR quantization scheme. *IEEE Trans. Electron Devices* **2013**, *60*, 2561–2566. [CrossRef]

- Park, H.; Yu, C.; Kim, H.; Roh, Y.; Burm, J. Low power CMOS image sensors using two step single slope ADC with bandwidthlimited comparators & voltage range extended ramp generator for battery-limited application. *IEEE Sens. J.* 2019, 20, 2831–2838. [CrossRef]

- Kim, M.K.; Hong, S.K.; Kwon, O.K. An area-efficient and low-power 12-b SAR/single-slope ADC without calibration method for CMOS image sensors. *IEEE Trans. Electron Devices* 2016, 63, 3599–3604. [CrossRef]

- 22. Zhang, Q.; Ning, N.; Zhang, Z.; Li, J.; Wu, K.; Yu, Q. A 12-bit two-step single-slope ADC with a constant input-common-mode level resistor ramp generator. *IEEE Trans. Very Large Scale Integr. VLSI Syst.* **2022**, *30*, 644–655. [CrossRef]

- Dai, S.; Hu, K.; Rosenstein, J.K. A segmented SAR/SS ADC with digital error correction and programmable resolution for column-parallel sensor arrays. In Proceedings of the 2020 IEEE International Symposium on Circuits and Systems (ISCAS), Seville, Spain, 12–14 October 2020; pp. 1–5. [CrossRef]

- 24. Lin, C.H.; Bult, K. A 10-b, 500-MSample/s CMOS DAC in 0.6 mm/sup 2. IEEE J. Solid-State Circuits 1998, 33, 1948–1958. [CrossRef]

- 25. Van Elzakker, M.; van Tuijl, E.; Geraedts, P.; Schinkel, D.; Klumperink, E.A.; Nauta, B. A 10-bit Charge-Redistribution ADC Consuming 1.9μW at 1 MS/s. *IEEE J. Solid-State Circuits* **2010**, *45*, 1007–1015. [CrossRef]

- Liu, C.C.; Huang, M.C.; Tu, Y.H. A 12 bit 100 MS/s SAR-assisted digital-slope ADC. *IEEE J. Solid-State Circuits* 2016, 51, 2941–2950. [CrossRef]

- 27. Liu, C.C.; Kuo, C.H.; Lin, Y.Z. A 10 bit 320 MS/s low-cost SAR ADC for IEEE 802.11 ac applications in 20 nm CMOS. *IEEE J. Solid-State Circuits* 2015, *50*, 2645–2654. [CrossRef]

- Wang, Z.; Liu, X.; Wan, P.; Chen, Z. Design of a column-parallel SAR/SS two-step hybrid ADC for sensor arrays. In Proceedings of the 2021 IEEE 15th International Conference on Anti-Counterfeiting, Security, and Identification (ASID), Xiamen, China, 29–31 October 2021; pp. 172–176. [CrossRef]

- McCreary, J.L.; Gray, P.R. All-MOS charge redistribution analog-to-digital conversion techniques. I. IEEE J. Solid-State Circuits 1975, 10, 371–379. [CrossRef]

- Promitzer, G. 12 bit low power fully differential switched capacitor non-calibrating successive approximation ADC with 1MS/s. In Proceedings of the 26th European Solid-State Circuits Conference, Stockholm, Sweden, 19–21 September 2000; pp. 176–179.

- Matsuo, S.; Bales, T.J.; Shoda, M.; Osawa, S.; Kawamura, K.; Andersson, A.; Haque, M.; Honda, H.; Almond, B.; Mo, Y.; et al. 8.9-megapixel video image sensor with 14-b column-parallel SA-ADC. *IEEE Trans. Electron Devices* 2009, 56, 2380–2389. [CrossRef]

- Kim, J.B.; Hong, S.K.; Kwon, O.K. A low-power CMOS image sensor with area-efficient 14-bit two-step SA ADCs using pseudomultiple sampling method. *IEEE Trans. Circuits Syst. II Express Briefs* 2015, 62, 451–455. [CrossRef]

- Zhang, Q.; Ning, N.; Li, J.; Yu, Q.; Zhang, Z.; Wu, K. A high area-efficiency 14-bit SAR ADC with hybrid capacitor DAC for array sensors. *IEEE Trans. Circuits Syst. I Regul. Pap.* 2020, 67, 4396–4408. [CrossRef]

- Moon, C.W.; Yoon, K.S.; Lee, J. A 12~14-Bit SAR-SS Hybrid ADC with SS Bit Shifting Resolution Reconfigurable Method for Bio-Signal Processing. *Electronics* 2023, 12, 4916. [CrossRef]

**Disclaimer/Publisher's Note:** The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.