# **High-Performance Distributed RMA Locks**

Patrick Schmid\*, Maciej Besta\*<sup>†</sup>, Torsten Hoefler

Department of Computer Science, ETH Zurich \*Both authors contributed equally to this work †Corresponding author

# ABSTRACT

We propose a topology-aware distributed Reader-Writer lock that accelerates irregular workloads for supercomputers and data centers. The core idea behind the lock is a modular design that is an interplay of three distributed data structures: a counter of readers/writers in the critical section, a set of queues for ordering writers waiting for the lock, and a tree that binds all the queues and synchronizes writers with readers. Each structure is associated with a parameter for favoring either readers or writers, enabling adjustable performance that can be viewed as a point in a three dimensional parameter space. We also develop a distributed topology-aware MCS lock that is a building block of the above design and improves stateof-the-art MPI implementations. Both schemes use non-blocking Remote Memory Access (RMA) techniques for highest performance and scalability. We evaluate our schemes on a Cray XC30 and illustrate that they outperform state-of-the-art MPI-3 RMA locking protocols by 81% and 73%, respectively. Finally, we use them to accelerate a distributed hashtable that represents irregular workloads such as key-value stores or graph processing.

# **CCS CONCEPTS**

• Hardware  $\rightarrow$  Testing with distributed and parallel systems; Networking hardware; • Computer systems organization  $\rightarrow$  Architectures; Parallel architectures; Multicore architectures; Distributed architectures; Multicore architectures; • Computing methodologies  $\rightarrow$  Parallel computing methodologies; Shared memory algorithms; Distributed algorithms; • Software and its engineering  $\rightarrow$  Synchronization; Access protection; • Theory of computation  $\rightarrow$  Parallel algorithms; Distributed algorithms; Shared memory algorithms; Distributed algorithms.

# This is an arXiv version of a paper published at ACM HPDC'16 under the same title

Code:

$https://spcl.inf.ethz.ch/Research/Parallel\_Programming/RMALocks$

# **1 INTRODUCTION**

The scale of today's data processing is growing steadily. For example, the size of Facebook's social graph is many petabytes [10, 50] and graphs processed by the well-known HPC benchmark Graph500 [40] can have trillions of vertices. Efficient analyses of such datasets require distributed-memory (DM) machines with deep *Non-Uniform Memory Access* (NUMA) hierarchies.

Locks are among the most effective synchronization mechanisms used in codes for such machines [9]. On one hand, if used improperly, they may cause deadlocks. Yet, they have intuitive semantics and they often outperform other schemes such as atomic operations [43] or transactions [6].

Designing efficient locks for machines with deep hierarchical memory systems is challenging. Consider four processes competing for the same lock. Assume that two of them (A and B) run on one socket and the remaining two (C and D) execute on the other one. Now, in a naive lock design oblivious to the memory hierarchy, the lock may be passed between different sockets up to three times, degrading performance (e.g., if the order of the processes entering the critical section (CS) is A. C. B. and D). Recent advances [12, 18] tackle this problem by reordering processes acquiring the lock to reduce inter-socket communication. Here, the order of A, B, C, and D entails only one inter-socket lock transfer, trading fairness for higher throughput. Extending such schemes to DM machines with weak memory models increases complexity. Moreover, expensive inter-node data transfers require more aggressive communicationavoidance strategies than those in intra-node communication [20]. To our best knowledge, no previous lock scheme addresses these challenges.

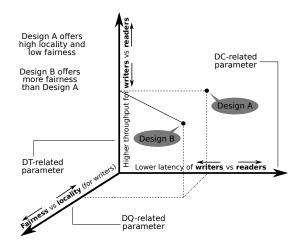

Figure 1: The space of parameters of the proposed Reader-Writer lock.

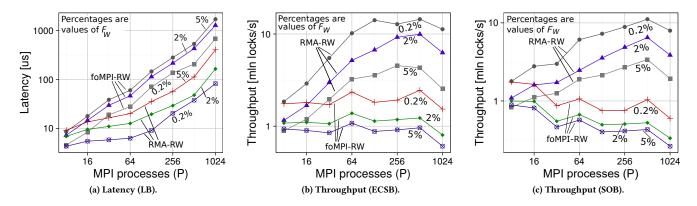

Another property of many large-scale workloads is that they are dominated by reads (e.g., they constitute 99.8% of requests to the Facebook graph [50]). Here, simple locks would entail unnecessary overheads. Instead, the Reader-Writer (RW) lock [38] can be used to reduce the overhead among processes that only perform reads in the critical section (CS). Initial RW *NUMA-aware* designs have recently been introduced [11], but they do not address DM machines.

In this work, we develop a lock that addresses the above challenges. Its core concept is a modular design for adjusting performance to various types of workloads. The lock consists of three key data structures. First, the distributed counter (DC) indicates the number of readers or the presence of a writer in the CS. Second, the distributed queue (DQ) synchronizes writers belonging to a given element of the memory hierarchy (e.g., a rack). Finally, the distributed tree (DT) binds together all queues at different levels of the memory hierarchy and synchronizes writers with readers. Each of these three structures offers an adjustable performance tradeoff, enabling high performance in various settings. DC can lower the latency of lock acquire/release performed by either readers or writers, DQ can be biased towards improving either locality or fairness, and DT can increase the throughput of either readers or writers. The values of these parameters constitute a three dimensional space that is illustrated in Figure 1. Each point is a specific lock design with selected performance properties.

Most DM machines offer Remote Direct Memory Access (RDMA) [42], a hardware scheme that removes the OS and the CPU from the inter-node communication path. RDMA is the basis of many Remote Memory Access (RMA) [20] programming models. Among others, they offer a Partitioned Global Address Space (PGAS) abstraction to the programmer and enable low-overhead direct access to remote memories with put/get communication primitives. RMA principles are used in various HPC languages and libraries: Unified Parallel C (UPC) [49], Fortran 2008 [30], MPI-3 [39], or SHMEM [4]. We will illustrate how to utilize RMA in the proposed locks for DM machines, addressing the above-mentioned challenges. In the following, we use MPI-3 RMA but we keep our protocols generic and we discuss (§ 6) how other RMA languages and libraries can also be used.

In summary, our key contributions are as follows:

- We develop a topology-aware distributed Reader-Writer lock that enables various tradeoffs between fairness, throughput, latency, and locality.

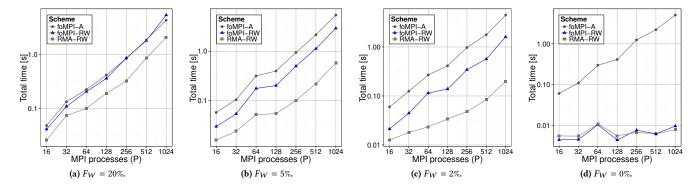

- We offer a topology-aware distributed MCS lock that accelerates the state-of-the-art MPI-3 RMA codes [20].

- We illustrate that our designs outperform the state-of-theart in throughput/latency (7.2x/6.8x on average) and that they accelerate distributed hashtables used in key-value (KV) stores or graph processing.

### 2 RMA AND LOCKS

We start by discussing RMA (§ 2.1), our tool to develop the proposed locks. Next, we present traditional (§ 2.2) and state-of-the-art (§ 2.3, § 2.4) locks that we use and extend.

**Notation/Naming:** We denote the number of processes as P; we use the notion of a *process* as it occurs frequently in DM codes such as MPI [39]. Still, our schemes are independent of whether heavyweight processes or lightweight threads are incorporated. Each process has a unique ID called the *rank*  $\in$  {1, ..., *P*}. A process in the CS is called *active*. A null pointer is denoted as  $\emptyset$ . Then, *N* is the number of levels of the memory hierarchy of the used machine. Here, the selection of the considered levels depends on the user. For example, one can only focus on the nodes connected with a network and racks that contain nodes and thus N = 3 (three levels:

the nodes, the racks, and the whole machine). We refer to a single considered machine part (e.g., a node) as an *element*. We refer to a node that is a shared-memory cache-coherent domain connected to other such domains with a non-coherent network as a *compute node* (or just *node*). One compute node may contain smaller elements that are cache-coherent and together offer *non-uniform memory access* (*NUMA*). We refer to such elements as *NUMA nodes*; an example NUMA node is a socket with a local DRAM. We present symbols used in the paper in Table 1.

| Р                                   | Number of processes.                                                                                                                                                                                                                              |  |  |  |  |  |  |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| p                                   | p Rank of a process that attempts to acquire/release a lock.<br>N Number of levels of the considered machine.<br>$i_i$ Number of machine elements at level $i$ ; $1 \le i \le N$ .<br>$i_i$ Index used to refer to the <i>i</i> th machine level. |  |  |  |  |  |  |

| Ñ                                   | Number of levels of the considered machine.                                                                                                                                                                                                       |  |  |  |  |  |  |

| $N_i$                               | i Number of machine elements at level $i$ ; $1 \le i \le N$ .                                                                                                                                                                                     |  |  |  |  |  |  |

| i                                   | <i>i</i> Index used to refer to the <i>i</i> th machine level.                                                                                                                                                                                    |  |  |  |  |  |  |

| j                                   | Index used to refer to the <i>j</i> th element at a given machine level.                                                                                                                                                                          |  |  |  |  |  |  |

| Table 1: Symbols used in the paper. |                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

## 2.1 RMA Programming

In RMA programming, processes communicate by directly accessing one another's memories. Usually, RMA is built over OS-bypass RDMA hardware for highest performance. RMA non-blocking *puts* (writes to remote memories) and *gets* (reads from remote memories) offer low latencies, potentially outperforming message passing [20]. Remote *atomics* such as compare-and-swap [24, 39] are also available. Finally, RMA *flushes* ensure the consistency of data by synchronizing respective memories. RDMA is provided in virtually all modern networks (e.g., IBM PERCS [3], IBM's on-chip Cell, InfiniBand [48], iWARP [21], and RoCE [29]). Moreover, numerous libraries and languages offer RMA features. Examples include MPI-3 RMA [39], UPC [49], Titanium [25], Fortran 2008 [30], X10 [14], or Chapel [13]. The number of RMA codes is growing steadily, and RMA itself is being continually enhanced [5, 7].

**RMA Windows:** In RMA, each process explicitly exposes an area of its local memory as shared. In MPI, this region is called a *window*. Once shared, a window can be accessed with puts/get-s/atomics and synchronized with flushes. We will refer to such an exposed memory in any RMA library/language as a window.

**RMA Functions:** We describe the syntax/semantics of the used RMA calls in Listing 1. All ints are 64-bit. For clarity, we also use the bool type and assume it to be an int that can take the 0 (false) or 1 (true) values, respectively. Values returned by Get/FAO/CAS are only valid after the subsequent Flush. The syntax is simplified for clarity: we omit a pointer to the accessed window (we use a single window). We use an *origin*/a *target* to refer to a process that issues or is targeted by an RMA call.

#### 2.2 Traditional Hardware-Oblivious Locks

We now present hardware-oblivious locks used in this work.

2.2.1 *Reader-Writer (RW) Locks.* Reader-Writer (RW) locks [15] distinguish between processes that only perform reads when in the CS (*readers*) and those that issue writes (*writers*). Here, multiple readers may simultaneously enter a given CS, but only one writer can be granted access at a time, with no other concurrent readers

```

1 /* Common parameters: target: target's rank; offset: an offset

into target's window that determines the location of the targeted data; op: an operation applied to a remote piece of

2

3

* data (either an atomic replace (REPLACE) or a sum (SUM));

* oprd: the operand of an atomic operation op.*/

/* Place atomically src_data in target's window.*/

8 void Put(int src_data, int target, int offset);

10 /* Fetch and return atomically data from target's window.*/

11 int Get(int target, int offset);

12

13 /* Apply atomically op using oprd to data at target.*/

14 void Accumulate(int oprd, int target, int offset, MPI_Op op);

15

16 /* Atomically apply op using oprd to data at target

17 * and return the previous value of the modified data.*/

18 int FAO(int oprd, int target, int offset, MPI_Op op);

19

20 /* Atomically compare cmp\_data with data at target and, if

* equal, replace it with src_data; return the previous data.*/

21

22 int CAS(int src_data, int cmp_data, int target, int offset);

24 /* Complete all pending RMA calls started by the calling process

25

and targeted at target.*/

26 void Flush(int target);

```

Listing 1: The syntax/semantics of the utilized RMA calls.

or writers. RW locks are used in OS kernels, databases, and present in various HPC libraries such as MPI-3 [39].

2.2.2 *MCS Locks.* Unlike RW locks, the MCS lock (due to Mellor-Crummey and Scott) [37, 44, 46] does not distinguish between readers or writers. Instead, it only allows one process p at a time to enter the CS, regardless of the type of memory accesses issued by p. Here, processes waiting for the lock form a queue, with a process at the head holding the lock. The queue contains a single global pointer to its tail. Moreover, each process in the queue maintains: (1) a local flag that signals if it can enter the CS and (2) a pointer to its successor. To enter the queue, a process p updates both the global pointer to the tail and the pointer at its predecessor so that they both point to p. A releasing process notifies its successor by changing the successor's local flag. The MCS lock reduces the amount of coherence traffic that limits the performance of spinlocks [2]. Here, each process in the queue spin waits on its local flag that is modified once by its predecessor.

#### 2.3 State-of-the-Art NUMA-Aware Locks

We now discuss lock schemes that use the knowledge of the NUMA structure of the underlying machine for more performance. We will combine and extend them to DM domains, and enrich them with a family of adjustable parameters for high performance with various workloads.

2.3.1 NUMA-Aware RW Locks. Many traditional RW locks (§ 2.2.1) entail performance penalties in NUMA systems as they usually rely on a centralized structure that becomes a bottleneck and entails high latency when accessed by processes from remote NUMA elements. Calciu et al. [11] tackle this issue with a flag on each NUMA node that indicates if there is an active reader on that node. This reduces contention due to readers (each reader only marks a local flag) but may entail additional overheads for writers that check for active readers.

2.3.2 Hierarchical MCS Locks. Hierarchical locks tackle expensive lock passing described in § 1. They trade fairness for higher

throughput by ordering processes that enter the CS to reduce the number of such passings. Most of the proposed schemes address two-level NUMA machines [12, 17, 34, 41]. Chabbi et al. consider a multi-level NUMA system [12]. Here, each NUMA hierarchy element (e.g., a socket) entails a separate MCS lock. To acquire the global lock, a process acquires an MCS lock at each machine level. This increases locality [47] but reduces fairness: processes on the same NUMA node acquire the lock consecutively even if processes on other nodes are waiting.

#### 2.4 Distributed RMA MCS Locks

Finally, we present a distributed MCS (D-MCS) lock based on an MPI-3 MCS lock [22]. We will use it to accelerate state-of-the-art MPI RMA library foMPI [20] and as a building block of the proposed distributed topology-aware RW and MCS locks (§ 3).

2.4.1 Summary and Key Data Structures. Here, processes that wait for the D-MCS lock form a queue that may span multiple nodes. Each process maintains several globally visible variables. A naive approach would use one window per variable. However, this would entail additional memory overheads (one window requires  $\Omega(P)$ storage in the worst case [20]). Thus, we use one window with different offsets determining different variables: a pointer to the next process in the MCS queue (offset NEXT, initially  $\emptyset$ ) and a flag indicating if a given process has to spin wait (offset WAIT, initially false). A selected process (rank tail\_rank) also maintains a pointer to a process with the queue tail (offset TAIL, initially  $\emptyset$ ).

*2.4.2 Lock Protocols.* We now describe the protocols for acquire/release. We refer to respective variables using their offsets in the window.

**Lock Acquire (Listing 2)** First, *p* atomically modifies TAIL with its own rank and fetches the predecessor rank (Line 6). If there is no predecessor, it proceeds to the CS. Otherwise, it enqueues itself (Line 10) and waits until its local WAIT is set to false. Flushes ensure the data consistency.

| 1  | <pre>void acquire() {</pre>                                       |

|----|-------------------------------------------------------------------|

| 2  | /* Prepare local fields. */                                       |

| 3  | $Put(\emptyset, p, NEXT);$                                        |

| 4  | Put( <b>true</b> , <i>p</i> , STATUS);                            |

| 5  | /* Enter the tail of the MCS queue and get the predecessor. */    |

| 6  | <pre>int pred = FAO(p, tail_rank, TAIL, REPLACE);</pre>           |

| 7  | Flush(tail_rank); /* Ensure completion of FAO. */                 |

| 8  | <pre>if(pred != ∅) { /* Check if there is a predecessor. */</pre> |

| 9  | /* Make the predecessor see us. */                                |

| 10 | <pre>Put(p, pred, NEXT); Flush(pred);</pre>                       |

| 11 | <pre>bool waiting = true;</pre>                                   |

| 12 | <pre>do { /* Spin locally until we get the lock. */</pre>         |

| 13 | <pre>waiting = Get(p, WAIT); Flush(p);</pre>                      |

| 14 | <pre>} while(waiting == true); } }</pre>                          |

Listing 2: Acquiring D-MCS.

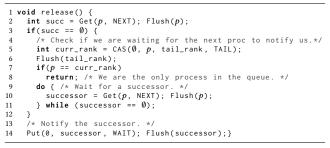

**Lock Release (Listing 3)** First, *p* checks if it has a successor in the queue (Line 3). If there is none, it atomically verifies if it is still the queue tail (Line 5); if yes, it sets TAIL to  $\emptyset$ . Otherwise, *p* waits for a process that has modified TAIL to update its NEXT field (Lines 9-11). If there is a successor, the lock is passed with a single Put (Line 14).

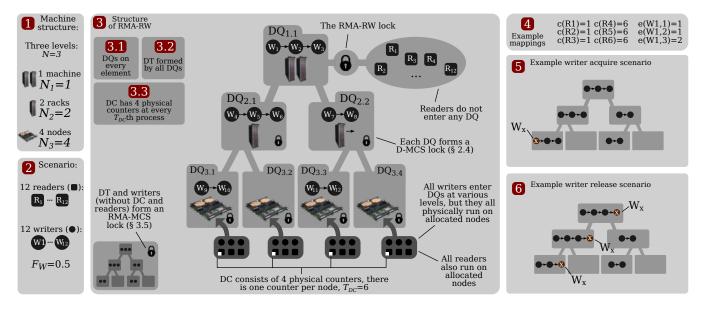

Figure 2: An example RMA-RW on a three-level system.

Listing 3: Releasing D-MCS.

## **3 DISTRIBUTED RMA RW LOCKS**

We now present a distributed *topology-aware* RW lock (RMA-RW) for scalable synchronization and full utilization of parallelism in workloads dominated by reads. We focus on the RW semantics as the key part of the introduced lock. Symbols specific to RMA-RW are presented in Table 2.

**Lock Abbreviations** We always refer to the proposed topologyaware distributed RW and MCS lock as RMA-RW and RMA-MCS, respectively. Both RMA-RW and RMA-MCS use as their building block a simple distributed topology-oblivious MCS lock (§ 2.4) denoted as D-MCS.

**Example** In the whole section, we will use the example shown in Figure 2. Here, N = 3 and the considered levels are: compute nodes, racks, and the whole machine.

#### 3.1 Design Summary and Intuition

As explained in § 1, RMA-RW consists of three types of core data structures: distributed queues (DQs), a distributed tree (DT), and a distributed counter (DC). They are illustrated in Figure 2. First, every machine element (at each considered level) has an associated DQ and thus a D-MCS lock *local* to this element (as opposed to

- $\begin{array}{l} T_{DC} \\ T_{L,i} \end{array} \left[ \begin{array}{c} \text{The Distributed Counter threshold (§ 3.2.1).} \\ \text{The Locality threshold at level } i \ (§ 3.2.2). \end{array} \right] \end{array}$

- $\overline{T_R}$  The *Reader* threshold (§ 3.2.3).

- $T_W$  The Writer threshold;  $T_W = \prod_{i=1}^N T_{L,i}$  (§ 3.2.3).

- c(p) Mapping from a process p to its physical counter (§ 3.2.1).

- e(p, i) Mapping from a process p to its home machine element at level i (§ 3.2.2).

- $F_W$  | The fraction of writers in a given workload (the fraction of readers:  $1 F_W$ ).

Table 2: Symbols used in RMA-RW.

the *global* RMA-RW lock). In our example, every node, rack, and the whole machine have their own DQ (and thus a local MCS lock). Note that some DQs that are associated with elements such as nodes are not necessarily distributed, but we use the same name for clarity. Second, all the DQs form a DT that corresponds to the underlying memory hierarchy, with one DQ related to one tree vertex. For example, DQs associated with nodes that belong to a given rack rconstitute vertices that are children of a vertex associated with a DQ running on rack r. Third, DC counts active readers and writers and consists of several physical counters located on selected processes. DT on its own (without DC and any readers) constitutes RMA-MCS.

**Writers** A writer that wants to acquire a lock starts at a leaf of DT located at the lowest level *N* (a node in our example). At any level i ( $2 \le i \le N$ ), it acquires a local D-MCS lock that corresponds to a subtree of D-MCS locks (and thus DQs) rooted at the given element. Here, it may compete with other writers. When it reaches level 1, it executes a different protocol for acquiring the whole RMA-RW lock. Here, it may also compete with readers. RMA-RW's locality-aware design enables a *shortcut*: some writers stop before reaching level 1 and directly proceed to the CS. This happens if a lock is passed within a given machine element.

**Readers** Readers do not enter DQs and DT and thus have a single acquire protocol. This design reduces synchronization overhead among readers.

#### 3.2 Key Data Structures

We now present the key structures in more detail.

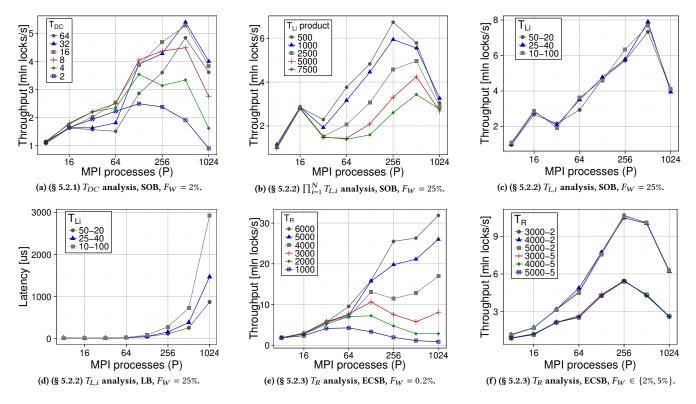

3.2.1 Distributed Counter (DC). DC maintains the number of active readers or writers. It enables an adjustable performance tradeoff that accelerates readers or writers. For this, one DC consists of multiple physical counters, each maintained by every  $T_{DC}$  th process;  $T_{DC}$  is a parameter selected by the user. To enter the CS, a reader p increments only one associated physical counter while a writer must check each one of them. Thus, selecting more physical counters (smaller  $T_{DC}$ ) entails lower reader latency (as each reader can access a counter located on a closer machine element) and contention (as each counter is accessed by fewer readers). Yet, higher  $T_{DC}$  entails lower latency for a writer that accesses fewer physical counters.

A physical counter associated with a reader *p* is located at a rank c(p);  $c(\cdot) \in \{1, ..., P\}$  can be determined at compile- or run-time. In a simple hardware-oblivious scheme, one can fix  $c(p) = \lceil p/T_{DC} \rceil$ . For more performance, the user can locate physical counters in a topology-aware way. For example, if the user allocates *x* processes/node and a node *s* hosts processes with *x* successive ranks starting from (s - 1)x + 1, then setting  $T_{DC} = kx$  in the above formula results in storing one physical counter every *k*th node. This can be generalized to any other machine element.

To increase performance, we implement each physical counter as two 64-bit fields that count the readers (assigned to this counter) that arrived and departed from the CS, respectively. This facilitates obtaining the number of readers that acquired the lock since the last writer and reduces contention between processes that acquire and release the lock. We dedicate one bit of the field that counts arriving readers to indicate whether the CS of RMA-RW is in the READ mode (it contains readers) or the WRITE mode (it contains a writer).

**RMA Design of DC:** Each physical counter occupies two words with offsets ARRIVE (for counting arriving readers) and DEPART (for counting departing readers); physical counters together constitute an RMA window.

3.2.2 Distributed Queue (DQ). DQ orders writers from a single element of the machine that attempt to enter the CS. DQs from level *i* have an associated threshold  $T_{L,i}$  that determines the maximum number of lock passings between writers running on a machine element from this level before the lock is passed to a process from a different element. We use a separate threshold  $T_{L,i}$  for each *i* because some levels (e.g., racks) may need more locality (a higher threshold) than others (e.g., nodes) due to expensive data transfers. This design enables an adjustable tradeoff between fairness and throughput at each level.

DQ extends D-MCS in that the local flag that originally signals whether a process can enter the CS now becomes an integer that carries (in the same RMA operation) the number of past lock acquires within a given machine element. We use this value to decide whether to pass the lock to a different element at a given level *i* (if the value reaches  $T_{L,i}$ ) or not (if the value is below  $T_{L,i}$ ).

**RMA Design of DQ:** All DQs at a given level constitute an RMA window. Respective offsets in the window are as follows: NEXT (a rank of the next process in the queue), STATUS (an integer that both

signals whether to spin wait and carries the number of past lock acquires in the associated machine element), and TAIL (a rank of the process that constitutes the current tail of the queue). TAIL in DQ at level *i* associated with *j*th element is stored on a process tail\_rank[*i*, *j*].

3.2.3 Distributed Tree of Queues (DT). DT combines DQs at different memory hierarchy levels into a single structure. This enables p to make progress in acquiring/releasing RMA-RW by moving from level N to level 1. Then, at the tree root, writers synchronize with readers. Specifically, the lock is passed from writers to readers (if there are some waiting) when the total number of lock passings between writers reaches a threshold  $T_W$ . In our design,  $T_W = \prod_{i=1}^N T_{L,i}$ . To avoid starvation of writers, we also introduce a threshold  $T_R$  that is the maximum number of readers that can enter the CS consecutively before the lock is passed to a writer (if there is one waiting). Increasing  $T_R$  or  $T_W$  improves the throughput of readers or writers because more processes of a given type can enter the CS consecutively.

While climbing up DT, a writer must determine the next DQ (and thus D-MCS) to enter. This information is encoded in a mapping  $e(\cdot, \cdot)$  and structure tail\_rank[i, j].  $e(p, i) \in \{1, ..., N_i\}$  returns the ID of a machine element associated with a process p at level i. An expression tail\_rank[i, e(p, i)] returns the rank of a process that points to the tail of a DQ at level i within a machine element assigned to p. This enables p to enter D-MCS at the next level on the way to the CS. Similarly to c(p), e(p, i) can be determined statically or dynamically.

Depending on  $T_{L,i}$ , some writers do not have to climb all DT levels and can proceed directly to the CS. Thus, we further extend the STATUS field used in DQ with one more special value ACQUIRE\_PARENT. This indicates that p cannot directly enter the CS and should continue up DT.

3.2.4 Discussion on the Status Field. A central part of DQ and DT is the STATUS field that enables processes to exchange various additional types of information in a single RMA communication action, including: (1) if a lock mode changed (e.g., from READ to WRITE), (2) if a given process should acquire a lock at a higher DT level, (3) if a given process can enter the CS, and (4) the number of past consecutive lock acquires. Two selected integer values are dedicated to indicate (1) and (2). All the remaining possible values indicate that the given process can enter the CS (3); at the same time the value communicates (4).

#### 3.3 Distributed Reader-Writer Protocol

We now illustrate how the above data structures play together in the acquire and release protocols. A writer starts at the leaf of DT (level *N*) both for acquiring and releasing. At any level *i*  $(2 \le i \le N)$ , it proceeds up the tree executing a protocol for a partial acquire/release of the respective part of the tree (§ 3.3.1, § 3.3.2). At level 1, it executes a different protocol for locking or releasing the whole lock (§ 3.3.3, § 3.3.4). Readers do not follow such a hierarchy and thus have single acquire (§ 3.3.5) and release (§ 3.3.6) protocols.

*3.3.1* Writer Lock Acquire: Level N to 2 (Listing 4). Intuition: p enters the DQ associated with a given level *i* and its home element

e(p, i); it then waits for the update from its predecessor. If the predecessor does not have to hand over the lock to a process from another element (i.e., has not reached the threshold  $T_{L,i}$ ), the lock is passed to p that immediately enters the CS. Otherwise, p moves to level i - 1.

**Details**: *p* first modifies its NEXT and STATUS to reflect it spin waits at the DQ tail (Lines 2-3). Then, it enqueues itself (Line 5). If there is a predecessor at this level, *p* makes itself visible to it with a Put (Line 8) and then waits until it obtains the lock. While waiting, *p* uses Gets and Flushes to check for any updates from the predecessor. If the predecessor reached  $T_{L,i}$  and released the lock to the parent level, *p* must itself acquire the lock from level i - 1 (Line 23). Otherwise, it can directly enter the CS as the lock is simply passed to it (Line 18). If there is no predecessor at level *i*, *p* also proceeds to acquire the lock for level i - 1 (Line 23).

```

1 void writer-acquire<i>() {

Put(\emptyset, p, NEXT);

Put(\emptyset, p, STATUS); Flush(p);

/* Enter the DQ at level i and in this machine element. */

3

int pred = FAO(p, tail_rank[i, e(p, i)], TAIL, REPLACE);

Flush(tail_rank[i, e(p, i)]);

if(pred != ∅) {

Put(p, pred, NEXT); Flush(pred); /* pred sees us. */

int status = WAIT:

10

do { /* Wait until pred passes the lock. */

status = Get(p, STATUS); Flush(p);

} while(status == WAIT);

11

12

/* Check if pred released the lock to the parent level. This

13

would happen if T_{L,i} is reached. */ if(status != ACQUIRE_PARENT) { /* <math display="inline">T_{L,i} is not reached. Thus, the lock is passed to

14

15

16

17

p that directly proceeds to the CS. */

18

return; /* The global lock is acquired. */

19

}

}

20

/* Start to acquire the next level of the tree.*/

21

Put(ACQUIRE_START, p, STATUS); Flush(p);

22

writer - acquire \langle i - 1 \rangle(); }

23

```

# Listing 4: Acquiring the RMA-RW lock by a writer; levels N to 2.

3.3.2 Writer Lock Release: Level N to 2 (Listing 5). Intuition: p passes the lock within e(p, i) if there is a successor and  $T_{L,i}$  is not yet reached. Otherwise, it releases the lock to the parent level i - 1, leaves the DQ, and informs any new successor that it must acquire the lock at level i - 1.

**Details:** *p* first finds out whether it has a successor. If there is one and  $T_{L,i}$  is not yet reached, the lock is passed to it with a Put (Line 8). If  $T_{L,i}$  is reached, *p* releases the lock for this level and informs its successor (if any) that it has to acquire the lock at level i - 1. If there is no known successor, it checks atomically if some process has already entered the DQ at level *i* (Line 15). If so, the releaser waits for the successor to make himself visible before it is notified to acquire the lock at level i - 1.

3.3.3 Writer Lock Acquire: Level 1 (Listing 7). Intuition: This scheme is similar to acquiring the lock at lower levels (§ 3.3.1). However, the predecessor may notify p of the *lock mode change* that enabled readers to enter the CS, forcing p to acquire the lock from the readers.

**Details**: p first tries to obtain the lock from a predecessor (Lines 2-18). If there is one, p waits until the lock is passed. Still, it can happen that the predecessor hands the lock over to the readers

```

void writer-release<i>() {

1

successor and get the local status. */

Check if there is a

int succ = Get(p, NEXT)

int status = Get(p, STATUS); Flush(p);

if(succ != \emptyset && status < T_{L,i}) {

4

/* Pass the lock to succ at level i as well as the number of past lock passings within this machine element. */

Put(status + 1, succ, STATUS); Flush(succ); return;

9

}

/* There is no known successor or the threshold at level i is

10

reached. Thus, release the lock to the parent level. */

writer-release<i-1>();

11

12

if(succ == 0) {

/* Check if some process has just enqueued itself. */

13

14

int curr_rank = CAS(\emptyset, p, tail_rank[i, e(p, i)], TAIL);

Flush(tail_rank[i, e(p, i)]);

15

16

17

if(p == curr_rank) { return; }

do { /* Otherwise, wait until suc

succ = Get(p, NEXT); Flush(p);

} while(succ == Ø);

18

succ makes itself visible. */

19

20

21

22

/* Notify succ to acquire the lock at level i-1. */

23

Put(ACQUIRE_PARENT, succ, STATUS); Flush(succ); }

```

# Listing 5: Releasing an RMA-RW lock by a writer; levels N to 2.

(Line 14). Here, *p* changes the mode back to WRITE before entering the CS (Line 16); this function checks each counter to verify if there are active readers. If not, it switches the value of each counter to WRITE (see Listing 6). If there is no predecessor (Line 19), *p* tries to acquire the lock from the readers by changing the mode to WRITE (Line 21).

```

1 /***** Change all physical counters to the WRITE mode *****/

2 void set_counters_to_WRITE() {

/* To simplify, we use one counter every T_{DC}th process.*/ for(int p = 0; p < P; p += T_{DC}) {

/* Increase the arrival counter

to block the readers.*/

Accumulate(INT64_MAX/2, p, ARRIVE, SUM); Flush(p);

7 } }

10 void reset_counter(int rank) {

11 /* Get the current values of the counters.*/

int arr_cnt = Get(rank, ARRIVE), dep_cnt = Get(rank, DEPART);

12

13

Flush(rank);

/* Prepare the values to be subtracted from the counters.*/

14

15

int sub_arr_cnt = -dep_cnt, sub_dep_cnt = -dep_cnt;

16

17

Make sure that the WRITE is reset if it was set.*/

18

if(arr_cnt >= INT64_MAX/2)

19

sub_arr_cnt -= INT64_MAX/2;

20

}

21

/* Subtract the values from the current counters.*/

Accumulate(sub_arr_cnt, rank, ARRIVE, SUM);

Accumulate(sub_dep_cnt, rank, DEPART, SUM); Flush(rank);

22

23

24 }

25

27 void reset_counters() {

28 for(int p = 0; p < P; p += T_{DC}) { reset_counter(p); } }

```

Listing 6: Functions that manipulate counters.

3.3.4 Writer Lock Release: Level 1 (Listing 8). Intuition: p first checks if it has reached  $T_W$  and if there is a successor waiting at level 1. If any case is true, it passes the lock to the readers and notifies any successor that it must acquire the lock from them. Otherwise, the lock is handed over to the successor.

**Details:** First, if  $T_W$  is reached, p passes the lock to the readers by resetting the counters (Line 6). Then, if it has no successor, it similarly enables the readers to enter the CS (Line 12). Later, p appropriately modifies the tail of the DQ and verifies if there is a new successor (Line 17). If necessary, it passes the lock to the successor

| 2      | <b>void</b> writer-acquire<1>() {<br>Put( $\emptyset$ , p, NEXT); Put(WAIT, p, STATUS);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3      | (F), i coperation of the second |

| 4      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6<br>7 | <pre>Flush(tail_rank[1, e(p, 1)]);</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 8      | <pre>if(pred != ∅) { /* If there is a predecessor*/</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 9      | <pre>Put(p, pred, NEXT); Flush(pred);</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 10     | <pre>int curr_stat = WAIT;</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 11     | <pre>do { /* Wait until pred notifies us.*/</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 12     | <pre>curr_stat = Get(p, STATUS); Flush(p);</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 13     | <pre>} while (curr_stat == WAIT);</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 14     | if(curr_stat == MODE_CHANGE) { /* The lock mode changed*/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 15     | /* The readers have the lock now; try to get it back.*/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 16     | <pre>set_counters_to_WRITE();</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 17     | <pre>Put(ACQUIRE_START, p, STATUS); Flush(p);</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 18     | } }                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 19     | else { /* If there is no predecessor*/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 20     | /* Change the counters to WRITE as we have the lock now.*/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 21     | <pre>set_counters_to_WRITE();</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 22     | <pre>Put(ACQUIRE_START, p, STATUS); Flush(p); } }</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

Listing 7: Acquiring an RMA-RW lock by a writer; level 1.

with a Put (line 23) and simultaneously (using next\_stat) notifies it about a possible lock mode change.

```

void writer-release<1>(){

1

bool counters_reset = false;

/* Get the count of consecutive lock acquires (level 1).*/

int next_stat = Get(p, STATUS); Flush(p);

if(++next_stat == T<sub>W</sub>) { /* Pass the lock to the readers.*/

reset_counters();/* See Listing 6.*/

next_stat = MODE_CHANGE; counters_reset = true;

int succ = Get(p, NEXT); Flush(p);

if(succ == 0) { /* No known successor.*/

if(!counters_reset) { /* Pass the lock to the readers.*/

reset_counters(); next_stat = MODE_CHANGE;/* Listing 6.*/

10

11

12

13

/* Check if some process has already entered the DQ.*/

int curr_rank = CAS(0, p, tail_rank[1, e(p, 1)], TAIL);

14

15

Flush(tail_rank[1,e(p, 1)]);

16

if(p == curr_rank) { return; } /* No successor...*/

do { /* Wait until the successor makes itself visible.*/

17

18

19

succ = Get(p, NEXT); Flush(p);

} while (succ == Ø);

20

21

/* Pass the lock to the successor.*/

22

Put(next_stat, succ, STATUS); Flush(succ); }

23

```

Listing 8: Releasing an RMA-RW lock by a writer; level 1.

3.3.5 *Reader Lock Acquire (Listing 9).* **Intuition:** Here, *p* first spin waits if there is an active writer or if *p*'s arrival made its associated counter c(p) exceed  $T_R$ . Then, it can enter the CS. If  $c(p) = T_R$ , then *p* resets DC.

**Details:** In the first part, p may spin wait on a boolean barrier variable (Line 5), waiting to get the lock from a writer. Then, p atomically increments its associated counter and checks whether the count is below  $T_R$ . If yes, the lock mode is READ and p enters the CS. Otherwise, either the lock mode is WRITE or  $T_R$  is reached. In case of the latter, p checks if there are any waiting writers (Line 17). If there are none, p resets the DC (Line 20) and re-attempts to acquire the lock. If there is a writer, p sets the local barrier and waits for DC to be reset by the writer.

*3.3.6 Reader Lock Release (Listing 10).* Releasing a reader lock only involves incrementing the departing reader counter.

1 void reader-release() { 2 Accumulate(1, c(p), DEPART, SUM); Flush(c(p)); }

Listing 10: Releasing an RMA-RW reader lock.

```

void reader-acquire() {

bool done = false; bool barrier = false;

while(!done) {

int curr_stat = 0;

if(barrier) {

do {

curr_stat = Get(c(p), ARRIVE); Flush(c(p));

} while(curr_stat >= T<sub>R</sub>);

10

11

/* Increment the arrival counter.*

12

13

barrier = true;

14

if(curr_stat == T_R) {/* We are the first to reach T_R */ /* Pass the lock to the writers if there are any.*/

15

16

int curr_tail = Get(tail_rank[1, e(p, 1)], TAIL);

17

Flush(tail_rank[1,e(p, 1)]);

if(curr_tail == 0) { /* There are no waiting writers.*/

18

19

20

21

reset_counter(c(p)); barrier = false;/* Listing 6.*/

}

22

}

/* Back off and try again.*/

Accumulate(-1, c(p), ARRIVE, SUM); Flush(c(p));

23

24

25

```

Listing 9: Acquiring an RMA-RW lock by a reader.

#### 3.4 Example

Consider the scenario from Figure 2. Here, there are three machine levels, 12 readers, and 12 writers ( $F_W = 0.5$ ).

Writer Acquire Assume a new writer  $W_x$  running on a node related to DQ3.1 attempts to acquire RMA-RW (Figure 2, Part 5). First, it enters DQ<sub>3.1</sub> (Listing 4). As this queue is not empty,  $W_x$ spins locally (Lines 10-12) until its predecessor  $W_9$  modifies  $W_x$ 's STATUS. Now, if  $W_9$  has not yet reached  $T_{L,3}$ ,  $W_x$  gets the lock and immediately proceeds to the CS (Lines 15-19). Otherwise, it attempts to move to level 2 by updating its STATUS (Line 22) and calling writer-acquire(i-1)). Thus, it enters DQ<sub>21</sub> and takes the same steps as in DQ<sub>3.1</sub>: it spins locally until W<sub>4</sub> changes its STATUS and it either directly enters the CS or it proceeds up to level 1. Assuming the latter,  $W_x$  enters DQ<sub>1,1</sub> and waits for  $W_1$  to change its STATUS (Listing 7, Lines 10-12). If STATUS is different from MODE\_CHANGE (Line 17),  $W_x$  can enter the CS. Otherwise, the lock was handed over to the readers and  $W_x$  calls set\_counters\_to\_WRITE() to change all physical counters to the WRITE mode (Line 15), which blocks new incoming readers. At some point, the readers reach the  $T_R$ threshold and hand the lock over to  $W_x$ .