# Improved RF Devices for Future Adaptive Wireless Systems Using Two-Sided Contacting and AlN Cooling

Lis K. Nanver, *Member, IEEE*, Hugo Schellevis, Tom L. M. Scholtes, Luigi La Spina, *Student Member, IEEE*, Gianpaolo Lorito, Francesco Sarubbi, Viktor Gonda, Miloš Popadić, Koen Buisman, *Student Member, IEEE*, Leo C. N. de Vreede, *Senior Member, IEEE*, Cong Huang, *Student Member, IEEE*, Silvana Milosavljević, and Egbert J. G. Goudena

Abstract—This paper reviews special RF/microwave silicon device implementations in a process that allows two-sided contacting of the devices: the back-wafer contacted Silicon-On-Glass (SOG) Substrate-Transfer Technology (STT) developed at DIMES. In this technology, metal transmission lines can be placed on the low-loss glass substrate, while the resistive/capacitive parasitics of the silicon devices can be minimized by a direct two-sided contacting. Focus is placed here on the improved device performance that can be achieved. In particular, high-quality SOG varactors have been developed and an overview is given of a number of innovative highly-linear circuit configurations that have successfully made use of the special device properties. A high flexibility in device design is achieved by two-sided contacting because it eliminates the need for buried layers. This aspect has enabled the implementation of varactors with special  $N_d x^{-2}$  doping profiles and a straightforward integration of complementary bipolar devices. For the latter, the integration of AlN heatspreaders has been essential for achieving effective circuit cooling. Moreover, the use of Schottky collector contacts is highlighted also with respect to the potential benefits for the speed of SiGe heterojunction bipolar transistors (HBTs).

Index Terms—Adaptive circuits, aluminum nitride deposition, bipolar junction transistors (BJTs), complementary bipolar silicon technology, heatspreaders, heterojunction bipolar transistors (HBTs), microwave devices, radio frequency (RF) circuits, Schottky collector contacting, selfheating, silicon-on-glass technology, substrate transfer, thermal instability, thermal resistance, thin-film heatspreaders, two-sided contacting, varactors, wireless systems.

# I. INTRODUCTION

T HAS long been recognized that the conventional conductive silicon substrate is highly unsuitable for RF applications. The solutions that have found their way to production are mainly combinations of high-resistivity Si and silicon-on-insulator (SOI) substrates [1], [2]. In particular, RF SOI CMOS is challenging the frequency territory of BiCMOS processes. The

Manuscript received January 09, 2009; revised April 08, 2009. Current version published August 26, 2009. This work has been supported in part by NXP/Philips Semiconductors Cluster and PACD projects. The circuit work is now also being continued in the context of the SmartMix MEMPHIS and SenterNovem projects, and process module development is being performed in cooperation with the STW TFN program and the FP6 D-DOTFET project.

The authors are with Laboratory of Electronic Components, Technology and Materials (ECTM), Delft Institute of Microsystems and Nanoelectronics (DIMES), Delft University of Technology, 2628 CT Delft, The Netherlands (e-mail: l.k.nanver@tudelft.nl).

Digital Object Identifier 10.1109/JSSC.2009.2023016

advantage of these types of processes is that they are a "small" modification of mainstream Si technology. A more aggressive approach is to entirely remove the silicon under the critical circuit regions. This can be achieved by local micromachining of the Si substrate [3] or by Substrate-Transfer Technology (STT) [4]–[6]. Besides the elimination of the lossy Si, another advantage of the actual removal of the Si up to the device regions can be the possibility of direct device contacting from the back of the wafer (the back-wafer). Such two-sided contacting has been achieved in the back-wafer contacted Silicon-On-Glass (SOG) technology being run at DIMES. This technology is an almost natural extension of RF SOI technology, which, instead of restricting the device architecture as in pure SOI processes, frees the device designer of the complications associated with making plugs and buried contacts.

In this paper, we review the devices already developed in back-wafer contacted SOG technology and comment on the potentials of technologies that allow two-sided contacting. In this STT, an almost fully-processed SOI circuit-wafer is transferred to glass by a gluing process and the bulk silicon is removed with the buried oxide (BOX) as etch-stop. In the original Philips version of this STT process, the active device was a novel lateral SOI NPN that used the BOX isolation layer to achieve a very low collector-base capacitance  $C_{BC}$  [4]. The transfer to glass also reduced the NPN substrate parasitics, but the main goal was to eliminate the Si under large passive elements. This process was developed in the beginning of the 1990s and was transferred to Philips Hamburg where it was industrialized [5]. At DIMES, the SOG process itself was developed further by adding full wafer-stepper patterning of the back of the wafer with process modules for near-ideal diode and low-ohmic contact fabrication. The first Si device focus was also on NPN fabrication for the reduction of  $C_{BC}$ : a bulk-Si vertical 25 GHz NPN was transferred to glass and the collector contacts were made directly under the emitter, thus minimizing  $C_{BC}$  and collector series resistance  $R_C$  [7]. Further developments included Schottky collector contacting, which, besides potential benefits for high-frequency operation, also simplifies the device structure even further. Both vertical NPNs and PNPs with Schottky collector contacts were fabricated in a complementary process, which is illustrative of how any simplification of the device architecture also facilitates the task of combining different device types in one process [8].

Although these bipolar device designs were successfully fabricated, circuit realizations were hampered by an extremely high thermal resistance of the transistors themselves. This was a direct consequence of the almost perfect electrical dielectric-isolation of the devices that, for the conventional dielectrics in Si technology, also implies (unfortunately) a very good thermal isolation. The thermal resistance of the devices can be extremely large: in some cases about 100 times larger than the comparable bulk-Si devices. The electrothermal investigation of these devices has been scientifically very rewarding and has led to new insights in the electrothermal behavior of bipolar transistors [9], [10]. However, for reliable integrated-circuit realizations, it is obviously imperative to have an effective thermal management of the devices. This has led to the development of deposited AlN layers as thin-film heatspreaders. We have with success integrated them on a device level and shown that they can bring the thermal resistance of the individual devices and the electrothermal behavior of small circuits into a domain that is suitable for reliable circuit fabrication [11].

Parallel with the bipolar SOG research, the development of a varactor IC technology was also undertaken. Unlike the bipolar circuits, the targeted circuit applications in the field of RF adaptivity did not have electrothermal issues, and, as a consequence, this process has reached a high level of maturity. In general, for RF/microwave varactors the research focus over the last years has been directed towards revolutionary microelectromechanical systems (MEMS) implementations [12]-[16] or new material integration, such as Barium Strontium Titanate (BST) [17], [18], but both options still suffer from performance problems. In general, RF MEMS solutions raise reliability and packaging questions that are seriously hampering their introduction in production. In contrast, with our more evolutionary SOG varactor technology, it has been possible to immediately demonstrate superior circuit performance. Consequently, a number of recordbreaking varactor-diode circuits have already been published and patented [19]-[27].

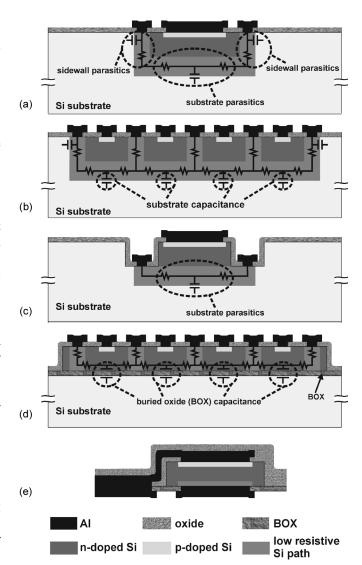

Besides very high quality factors (Q), the SOG varactor circuits have excelled with respect to linearity. In particular, special  $N_d x^{-2}$  doping profiles, where  $N_d$  is the maximum doping concentration and x the depth, have been developed and implemented in novel low-distortion circuit configurations. For the preservation of these profiles during processing, the subsequent thermal budget must be low. This is not an issue in the SOG process since no buried contacts are needed. In a bulk realization, not only the thermal budget but also the series resistance to the buried contacts represents a problem: low RC parasitics can only be achieved by using finger-like structures that have the drawback of seriously complicating the control of the doping profile that determines the varactor's C-V characteristic. With back-wafer contacting, the metal contact can be placed directly next to the capacitor and, in this manner, the ideal intrinsic 1-D device performance is approached. To emphasize this great advantage of the two-sided contacting, a comparison in terms of RC parasitics to a few other, more typical, isolation strategies is given in the simplistic schematics of Fig. 1 and the associated Table I. The extremely low parasitics in the SOG version

Fig. 1. Comparison of different isolation schemes for a diode processed as (a) a single-finger, (b) multi-finger or (c) trench-isolated device on bulk Si with buried layer, (d) a multi-finger device in SOI, and (e) a two-side contacted device as fabricated in SOG technology.

has meant that circuit concepts can be realized that are much simpler and more potent than otherwise feasible. For example, several very low-distortion varactor configurations for RF adaptivity have been realized and these are reviewed in relationship to the design strategies.

In the last section, we focused on the potentials of the SOG process. This includes comments on the advantages and disadvantages of using a more conservative micromachining approach to two-sided contacting.

# II. HIGH-PERFORMANCE VARACTORS

# A. Ultra-Low Distortion Varactor Configurations

Next-generation wireless systems, such as multi-mode transceivers and "cognitive radios", require circuit techniques that facilitate RF adaptivity. An ideal tuning element for these applications will exhibit extremely low loss, low dc power consumption, high linearity, ruggedness to high voltage and high current, wide tuning range, high reliability, very low cost, low area usage, and continuous tunability with a high tuning speed. To meet these stringent requirements, different varactor diodebased circuit topologies—along with a dedicated high-performance SOG varactor process technology—have been developed and implemented. These proposed varactor configurations can act as variable capacitors between their RF terminals with ideally zero, or extremely low distortion. A brief description of these low-distortion varactor configurations is given below.

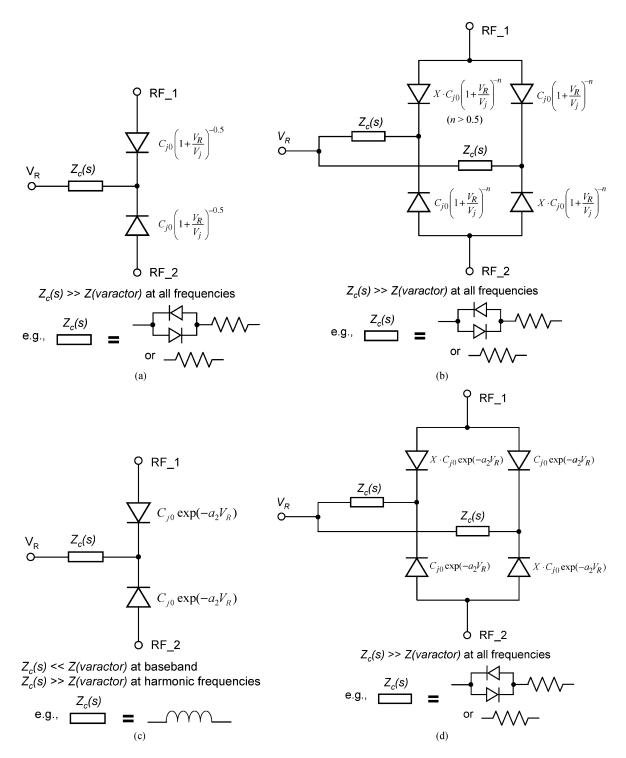

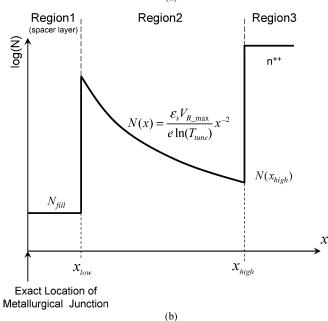

- The distortion-free varactor stack [20], [21] is based on an anti-series connection of two identical uniformly doped diodes as shown in Fig. 2(a). A capacitance power law coefficient of n = 0.5 [28] is applied along with an infinitely high impedance as center-tap connection. Under these conditions, all distortion components at the RF terminals are perfectly canceled, yielding a distortion-free operation.

- The high tuning range varactor stack [21] is a combined anti-series/anti-parallel topology of four hyperabrupt varactor diodes [28] as shown in Fig. 2(b). A capacitance power law coefficient n>0.5 is applied along with two infinitely high center-tap impedances. At the RF terminals, the resulting even and third-order distortion products are canceled through a proper selection of the varactor area ratio X [see Fig. 2(b)].

- The narrow tone-spacing varactor stack [21]–[23] is based on an anti-series connection of two  $N_d x^{-2}$  doped diodes as shown in Fig. 2(c). Note that this special doping profile results in exponential  $C(V_R)$  behavior under reverse bias  $V_R$ . To cancel the third-order intermodulation distortion  $(IM_3)$ , there must be a low impedance path (relative to the AC impedance of the varactor capacitance itself) between the center node  $(V_R)$  and the two RF terminals at low frequencies. At the same time, the high-frequency components (fundamental and higher harmonics) at the center tap node should experience a high impedance, i.e.,  $Z_c(s)$ should be much larger than the AC impedance of the varactor diode itself at these frequencies. When these conditions are met, the  $IM_3$  will be cancelled and the remaining distortion is dominated by the much smaller fifth-order nonlinearity.

- The wide tone-spacing varactor stack [23] is a combined anti-series/anti-parallel topology of four  $N_dx^{-2}$  doped diodes as shown in Fig. 2(d), which use an infinitely high impedance as center-tap connection. It can be regarded as a special case of the high tuning range varactor stack when the capacitance power law coefficient, n, approaches infinity, with the corresponding varactor area ratio of  $2 \pm \sqrt{3}$ . It shares the same doping profile as the narrow tone-spacing varactor stack and therefore both configurations (wide- and narrow-tone-spacing varactor stacks) can be implemented on the same wafer while offering complementary linearity properties in terms of tone spacing.

The different varactor configurations treated above, all provide a (center-tap) voltage-controlled tunable capacitance, which behaves linearly between the RF terminals provided that the appropriate combination of varactor doping profile, area ratio and center-tap termination is implemented. The differences between various varactor configurations are listed

in Table II, which summarizes the topology,  $C(V_R)$  relation, doping profile, harmonic conditions, area ratio for  $IM_3$  cancellation and the resulting linearity at  $IM_3$  frequencies for different tone-spacing regimes.

Note that the varactor configurations that feature infinitely high center-tap impedance(s) provide the best linearity for signals that have a relatively large frequency spacing (several hundred kilohertz). This property makes these configurations most suited for (adaptive) receiver applications where cross modulation of the "weak" desired signals by strong out-of-band interferers should be avoided. In (adaptive) transmitting systems, however, the in-band linearity will be the biggest concern. For these applications the narrow tone-spacing varactor stack [22] is recommended, since it provides the highest linearity for in-band signals (up to ten's of MHz's). Moreover, the fact that this latter configuration makes use of a base-band "short" (typically an inductor) connection to the varactor stack center-tap facilitates rapid modulation of its tunable capacitance, something that is beneficial for future RF applications like dynamic load-line power amplifiers or modulators.

It must be mentioned that the varactor configurations that make use of an "infinitely" high center-tap impedance can be linked to each other by considering the required area ratio for  $IM_3$  cancellation. For example, for the high tuning-range varactor stack [21] with the corresponding doping profile  $N_d x^{(1/n)-2}$ , the appropriate area ratio for  $IM_3$  cancellation is

$$X = \frac{4n+1+\sqrt{12n^2-3}}{2(n+1)}. (1)$$

When setting the capacitance power law coefficient n to 0.5, the resulting X will be unity and therefore the two anti-series branches will be identical, which means that, in practice, the high tuning range varactor stack can be reduced to the distortion-free varactor stack configuration [21] [Fig. 2(b) simplifies to Fig. 2(a)]. On the other hand, when  $n = \infty$ , the corresponding doping profile and area ratio for  $IM_3$  cancellation will be  $N_d x^{-2}$  and  $X = 2 + \sqrt{3}$ , which is identical to the configuration of wide tone-spacing varactor stacks [23] as specified in Table II [Fig. 2(d) same as Fig. 2(b)]. From this perspective, both the distortion-free varactor stack and wide tone-spacing varactor stack can be regarded as special cases of the high tuning range varactor stack, which implies that these two topologies preserve all the merits of the high tuning range varactor stack. Closer inspection, however, shows that the distortion-free varactor stack has the unique property that it is basically free of all distortion in the high tone-spacing regime. In comparison, the high tuning range varactor stack and the wide-tone spacing varactor stack are limited by  $IM_5$  products with respect to linearity. When considering the tuning range, the uniform doping of distortion-free varactor stacks has a relatively fixed relationship between the tuning range and control voltage, which is not the case for the other configurations due to the free-to-choose grading coefficient ( $a_2$  or n of  $C(V_R)$ , see Table II). This flexibility in grading facilitates easy adjustment of the tuning range and control voltage range for a given application.

As far as integration is concerned, the wide tone-spacing varactor stack can be easily integrated with the narrow tone-spacing varactor stack since they can share the same doping profile.

Fig. 2. (a) Configuration of the distortion-free varactor stack. (b) Configuration of high tuning range varactor stack. (c) Configuration of the narrow tone-spacing varactor stack. (d) Configuration of the wide tone-spacing varactor stack. Note that Z(varactor) represents the AC impedance of the capacitance offered by a single varactor in the stack.

Therefore the different linearity requirements of transmit and receive chains can be addressed in one single technology [23].

# B. High-Performance Varactor Diode Implementation

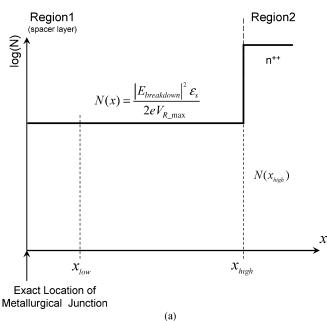

1) Doping Profile and Quality Factor Optimization: In order to achieve the capacitance power law coefficient of 0.5 for the distortion-free varactor stack, a uniform doping

profile is required as shown Fig. 3(a). This doping concentration needs to be chosen carefully since this sets the quality factor and device breakdown. When the desired tuning range  $(T_{tune} = C_{max}/C_{min})$  where  $C_{max}$  and  $C_{min}$  are the maximum and minimum capacitance values, respectively) is known, together with the material parameters, like maximum electric field  $(E_{breakdown})$ , dielectric constant  $(\varepsilon_s)$ , mobility  $(\mu_n)$  and

TABLE I COMPARISON OF THE PARASITIC RESISTANCE R and Capacitance C for Different Isolation Schemes as Illustrated in Fig. 1. The  $C=C_{sw}+C_{sub}$ , Where  $C_{sw}$  and  $C_{sub}$  are Sidewall and Substrate Components, Respectively

| Device type           | R                                              | $C_{sw}$                               | C <sub>sub</sub>                          | Comments                                                                                |

|-----------------------|------------------------------------------------|----------------------------------------|-------------------------------------------|-----------------------------------------------------------------------------------------|

| (a) bulk              | $R_{bulk} = R_{bulk}^{sw} + R_{bulk}^{sub}$    | $C^{sw}_{bulk}$                        | $C^{sub}_{bulk}$                          | + doping-profile degraded<br>by high-temperature<br>processing                          |

| (b) multi-finger bulk | $R_{multi} < R_{bulk}$                         | $C_{multi}^{sw} \approx C_{bulk}^{sw}$ | $C_{multi}^{sub} > C_{bulk}^{sub}$        | + n fingers: R ≈ 1/n,<br>+ large diode perimeter ⇒<br>poor doping-profile<br>control    |

| (c) trench-isolated   | $R_{trench} \approx R_{bulk}^{sub} < R_{bulk}$ | 0                                      | $C_{trench}^{sub} \approx C_{bulk}^{sub}$ | + no high-temperature plug processing                                                   |

| (d) multi-finger SOI  | $R_{SOI} > R_{multi}$                          | 0                                      | $C_{OX}$                                  | no low-resistive path to<br>region beneath the diode,<br>poor doping-profile<br>control |

| (e) 2-side contacted  | 0                                              | 0                                      | 0                                         | + lossy substrate eliminated + 1-D diode, + good doping-profile control                 |

TABLE II

OVERVIEW OF NARROW TONE-SPACING VARACTOR STACK, WIDE TONE-SPACING VARACTOR STACK,

DISTORTION-FREE VARACTOR STACK AND HIGH TUNING RANGE VARACTOR STACK

|                                           | Topology                                      | $C(V_R)$ Relation                                            | Doping<br>Profile                                      | Center-Tap Impedance $[Z_c(S) \text{ in Fig.2}]$             | Area Ratio (X)<br>for IM <sub>3</sub><br>Cancellation | Linearity<br>at 2f <sub>1</sub> -f <sub>2</sub><br>and 2f <sub>2</sub> -f <sub>1</sub> |

|-------------------------------------------|-----------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------|

| distortion-free<br>varactor stack         | anti-series<br>[Fig. 2 (a)]                   | $C_{j0} \left( 1 + \frac{V_R}{V_j} \right)^{-0.5}$           | N <sub>uniform</sub><br>constant                       | infinity for all frequencies                                 | 1:1                                                   | for large $\Delta f$ free of distortion                                                |

| high tuning range<br>varactor stack       | anti-series/<br>anti-parallel<br>[Fig. 2 (b)] | $C_{j0} \left( 1 + \frac{V_R}{V_j} \right)^{-n}$ $(n > 0.5)$ | $\frac{N_d x^{n-2}}{(n > 0.5)}$ (n > 0.5) hyper-abrupt | infinity for all frequencies                                 | $\frac{4n+1+\sqrt{12n^2-3}}{2(n+1)}$                  | for large $\Delta f$<br>$IM_3$ cancelled<br>$IP_5 = 2.72(V_R + V_j)$<br>(n = 1, X = 2) |

| narrow tone-<br>spacing varactor<br>stack | anti-series<br>[Fig. 2 (c)]                   | $C_{j0} \exp(-a_2 V_R)$                                      | $N_d x^{-2}$                                           | zero at low<br>frequency<br>infinity at other<br>frequencies | 1:1                                                   | for small $\Delta f$ $IM_3 \text{ cancelled}$ $IP_5 = \frac{3.52}{a_2}$                |

| wide tone-<br>spacing varactor<br>stack   | anti-series/<br>anti-parallel<br>[Fig. 2 (d)] | $C_{j0} \exp(-a_2 V_R)$                                      | $N_d x^{-2}$                                           | infinity for all frequencies                                 | $2\pm\sqrt{3}$                                        | for large $\Delta f$ $IM_3 \text{ cancelled}$ $IP_5 = \frac{2.75}{a_2}$                |

Symbols:  $C_{j0}$  is the capacitance at zero bias;  $\Delta f$  is the frequency difference or tone spacing of two-tone input RF signals and  $IP_5$  is the fifth-order interception point at  $2f_1 - f_2$  and  $2f_2 - f_1$  (Note that  $IM_3$  is cancelled while a much smaller  $IM_5$  remains).

built-in potential  $(V_j)$ , the best choice for the doping concentration  $(N_{uniform})$  can be selected using

With this selection, the related highest theoretically achievable quality factor for the varactor at zero bias operation is defined as

$$N_{uniform} = \frac{\varepsilon_s E_{breakdown}^2}{2eV_j \left(T_{tune}^2 - 1\right)}$$

$$(2) \qquad Q_{uniform}|_{V_R=0} = \frac{\mu_n E_{breakdown}^2}{2\omega V_j \left(T_{tune}^2 - 1\right) \left(T_{tune} - 1\right)}$$

$$(3)$$

where e is the electron charge.

where  $\omega$  is the angular RF frequency.

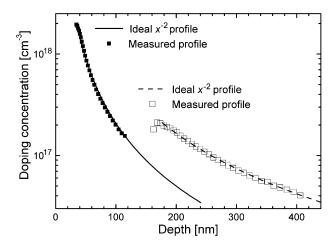

Fig. 3. (a) Optimized doping profile of the uniform doped diode for the distortion-free varactor stack. (b) Optimized doping profile for the narrow tone-spacing varactor stack and wide tone-spacing varactor stack to achieve the exponential  $C(V_R)$  relation.

For the narrow tone-spacing varactor stack and wide tone-spacing varactor stack, the required  $N_d x^{-2}$  doping profile, which provides the exponential  $C(V_R)$  relationship, is shown in Fig. 3(b). Since we cannot implement infinitely high or extremely low doping concentrations, the  $N_d x^{-2}$  relationship is restricted between  $x_{low}$  and  $x_{high}$ , which automatically defines the useful capacitance tuning range. To maintain the "exponential"  $C(V_R)$  relation and avoid reduced breakdown voltage and quality factor, a lowly doped spacer layer [Region 1 in Fig. 3(b)] is required. In contrast to the uniformly doped case, here for a free-to-choose combination of tuning range

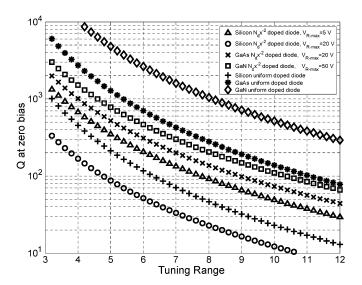

Fig. 4. The maximum achievable quality factors at zero bias for the uniform doped diode and  $N_d x^{-2}$  doped diode with different technology implementations. (For silicon,  $\mu_n = 1000 \text{ cm}^2/(\text{V} \cdot \text{s})$ ,  $E_{breakdown} = 6 \times 10^5 \text{ V/cm}$ ; for GaAs,  $\mu_n = 6000 \text{ cm}^2/(\text{V} \cdot \text{s})$ ,  $E_{breakdown} = 6 \times 10^5 \text{ V/cm}$ ; for GaN,  $\mu_n = 900 \text{ cm}^2/(\text{V} \cdot \text{s}), E_{breakdown} = 3 \times 10^6 \text{ V/cm}.$

and maximum reverse applied voltage  $(V_{R\_max})$ , the quality factor can be optimized by dimensioning the doping profile. The resulting doping profile and maximum achievable quality factors at zero bias for these structures can be written as [24]

$$N(x) = \frac{\varepsilon_s V_{R_{-} \max}}{e \ln(T_{tune})} x^{-2} \tag{4}$$

$$Q|_{V_R=0} = \frac{3\mu_n \ln(T_{tune})}{\omega V_{R-\max}(T_{tune}^3 - 1)} \left(\frac{T_{tune}E_{breakdown}}{T_{tune} - 1}\right)^2. (5)$$

The resulting maximum achievable quality factors at zero bias are plotted as a function of  $T_{tune}$  in Fig. 4 for different technology implementations. Due to the fact that the optimized quality factor is proportional to  $\mu_n$  and to the square of  $E_{breakdown}$ , the quality factor of these devices can be improved through the use of high-mobility or wide-bandgap materials; e.g., in GaAs an enhancement factor of 6-8 is feasible since  $\mu_n = 6000 \,\mathrm{cm}^2(\mathrm{V}\cdot\mathrm{s})$  and  $E_{breakdown} = 6 \times 10^5 \,\mathrm{V/cm}$  [28], and in GaN even a factor of 25 is possible with  $\mu_n = 900 \, \mathrm{cm}^2/(\mathrm{V} \cdot \mathrm{s})$ and  $E_{breakdown} = 3 \times 10^6$  V/cm [29]. Also multi-stacking of the low-distortion varactor configurations can be considered to achieve a higher RF-voltage handling while still maintaining a high quality factor [20].

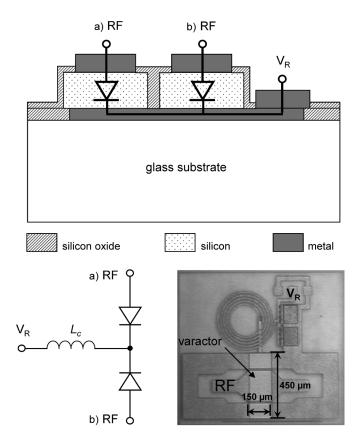

2) SOG Varactor Implementations: In the SOG varactor process the varactor diode itself is a very straightforward "one-dimensional" structure, for which the advantages of the two-sided contacting are over-evident. Using this feature, the intrinsic varactor can be directly contacted by thick metal interconnects on both sides as shown in Fig. 5. This eliminates the need for finger structures as typically used in conventional varactor implementations to lower the influence of the buried layer series resistance. The remaining losses of the metal interconnects can be significantly reduced through the use of plated copper, facilitating very high quality factors. Substrate losses are eliminated by the perfect isolating properties of the

Fig. 5. Cross section, equivalent schematic, and layout of a 33 pF varactor stack implemented in SOG technology with metal interconnects on both sides.

glass carrier, while due to low dielectric constant of glass also the influence of parasitic shunt capacitances are reduced.

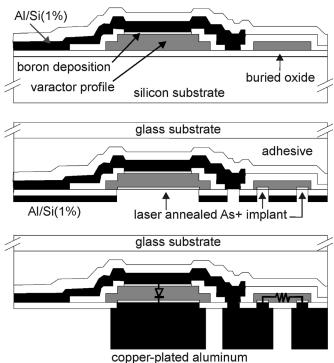

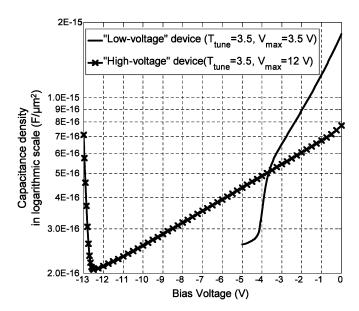

The basics of the actual SOG process flow are illustrated in Fig. 6. Our starting material is 100 mm SOI SOITEC wafers on which any extra Si layers needed for the specific device fabrication are grown epitaxially. The varactor profiles are tailored to the application by arsenic doping-profile engineering during the epitaxy. The total n-epi thickness depends on the breakdown voltage that is required. Examples of the realized "high-voltage" and "low-voltage"  $N_d x^{-2}$  doping profiles are shown in Fig. 7.

After epitaxy, the diode and resistor Si-islands are defined by plasma etching of shallow-trench steps to the BOX. The varactor diode p<sup>+</sup> terminal contact windows are processed and contacted by Al/Si(1%) metal tracks after which the metallization stack in which other passives are formed is processed. The wafer is covered with 1  $\mu$ m PECVD oxide to enable the gluing of the wafer to a glass wafer. To preserve the integrity of the adhesive, all subsequent thermal processing temperatures must not exceed 300 °C. After gluing, the Si substrate is removed by etching selectively to the BOX. An Al layer is sputtered on the back-wafer to serve as a reflective mask for laser annealing and the back-wafer contact windows are then etched through the Al and BOX. The contacts are implanted with 5 keV As<sup>+</sup> and excimer laser annealed for dopant activation. In this manner it is possible to create low-ohmic contacts and near-ideal diodes essentially at "room-temperature" [30], [31]. This is because the laser pulse only melts the top few nm of the Si surface while the

Fig. 6. Schematic of process flow for the integration of SOG varactor diodes and high-ohmic resistors.

Fig. 7. Two examples of the experimental  $N_dx^{-2}$  doping profiles (high- and low-voltage) as extracted from  $C-V_R$  measurements and compared to the theoretically desired profile.

heat pulse that thereby is sent into the bulk is so short, in the  $\mu s$  range at most, that the underlying layers are unaffected. This step provides the low-ohmic contact to the back of the diodes as well as contacts to the resistors. Next, the contact windows to the front-wafer metal are etched and Al/Si(1%) is sputtered and patterned on the back-wafer. Electroplating of 4- $\mu m$ -thick copper on the Al is then performed to achieve low metal resistance.

3) Experimental Results: Using the ability to adjust the  $C-V_R$  relationship by the doping profile, to achieve the desired capacitance control range and related control voltage, the needs of various practical applications can be addressed. Consequently,

Fig. 8. Measured  $C-V_R$  relations for "low-voltage" phase shifter and "high-voltage" matching network implementations. These results demonstrate that  $C-V_R$  dependency realized in the SOG technology can be adjusted to the requirements of the application.

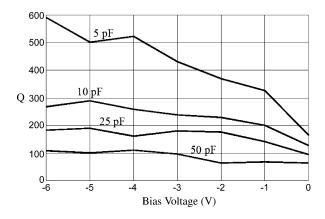

Fig. 9. The measured non-deembedded Q is plotted versus center-tap control voltage at 2 GHz for a copper-plated SOG distortion-free varactor-stack with zero-biased capacitances of 5, 10, 25, and 50 pF. This measurement result shows that very large Q can be obtained also for large varactors [20].

"low-voltage" [23] and "high voltage devices" [23] have been implemented as shown in Fig. 8.

Using the SOG varactor technology, ultra-low distortion tunable capacitive devices have been fabricated, which show record-high Q values (Q>200 @ 2 GHz for large capacitance values [21]), as shown in Fig. 9. As can be seen, high Q can be obtained also for the very large capacitance values due to the back-wafer contacting and copper-plating.

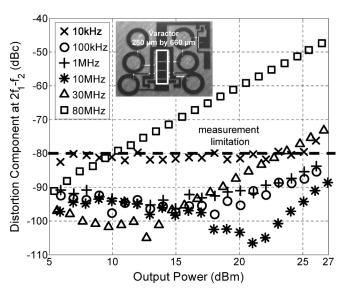

Multi-stacking yielded a record high linearity for a continuously tunable capacitive device [22] with an output third-order interception point  $(OIP_3) > 67$  dBm, as illustrated in Fig. 10. It is noteworthy that the  $IM_3$  level of the devices below a tone-spacing of 30 MHz basically cannot be measured since it requires an even higher dynamic range than offered by the dedicated test bench [32]. Conservatively speaking, the measured  $OIP_3$  is larger than 67 dBm up to 10 MHz bandwidth, which is

Fig. 10. Multi-stacked narrow-tone spacing varactor configuration with measured two-tone  $IM_3$  ( $f_{\rm center}=2$  GHz) linearity as function of output power [21]. Note that, below the linearity level of -80 dBc, it is difficult to separate the nonlinearities resulting from the varactors from that of the measurement setup, and therefore a conservative boundary of trust is marked as "measurement limitation".

TABLE III

LINEARITY COMPARISON OF CURRENTLY AVAILABLE TUNABLE ELEMENTS

| Technology                    | Input Third-order Intercept Point (dBm) |  |

|-------------------------------|-----------------------------------------|--|

| MEMS Switch                   | 66-80 [33]                              |  |

| MEMS Varactor*                | 44 [34]                                 |  |

| PIN diode*                    | 27-45 [33]                              |  |

| FETs <sup>*</sup>             | 27-45 [33]                              |  |

| Ferroelectric based varactor* | 50 [35]                                 |  |

| This work <sup>*</sup>        | > 67 [21]                               |  |

<sup>\*</sup> continuously tunable elements

the highest value ever reported for a continuously tunable capacitive device and which is comparable to that of MEMS switched devices (see the comparison in Table III [33]–[35]).

# C. Adaptive RF Circuits Using Varactor-Based Adaptive Circuits

In modern telecommunication systems there is a great need for technologies and circuits that enable adaptive RF functionality. Note that such a flexible RF functionality is desired to handle the ever increasing number of wireless services with a limited number of RF transceiver hardware line-ups. Desired functions include tunable filters, matching networks, and phase shifters. Common requirements to these networks are that they should be low loss and do not introduce any signal distortion. Consequently, the SOG technology in combination with low-distortion varactor configurations is an interesting candidate to fulfill these needs. This is endorsed by a number of varactor-

based circuit demonstrators fabricated over the last years, examples of which are given below.

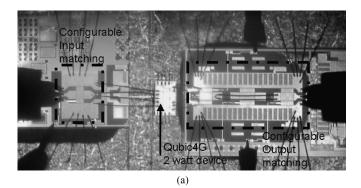

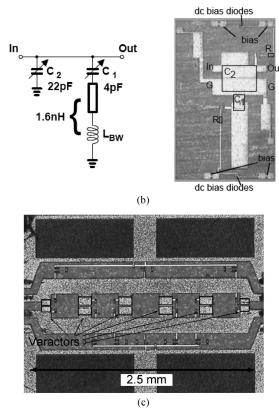

In [24], an adaptive multi-band, multi-mode power amplifier is presented, that can change continuously in operating frequency, while offering load-line adjustment to enhance the efficiency of the output stage when operating in output power backoff. The tunable varactor-based matching networks used in this demonstrator as shown in Fig. 11(a) exhibit third-order interception point (IIP<sub>3</sub>) better than +42 dBm, while able to tune the loading condition from 0.2 to 82  $\Omega$ . The amplifier demonstrator including these tunable matching networks provides 13 dB gain at 27–28 dBm output power and covers the 900, 1800, 1900, and 2100 MHz bands. In addition, the amplifier provides improved efficiency in power back-off by load line adjustment.

An example of a tunable bandpass filter based on the low-distortion varactor concepts in SOG technology is given in Fig. 11(b) [24]. The fabricated transmit-reject filter can be tuned from 2.4 to 3.5 GHz with a passband loss of 2–3 dB, a stopband rejection of 25 dB and an  $IIP_3$  of +46 dBm.

Note that the linearity and voltage handling of all these circuits can be further improved by stacking multiple varactors in series at the expense of increased area usage [25], doing so,  $IIP_3$  values above +60 dBm have been demonstrated. In addition to the obvious need in wireless applications for adaptive matching networks and tunable filters, the growing popularity of phase diversity systems also yields an increased interest in phase shifters. In these later systems the phase of each individual antenna element is controlled to steer the radiation pattern of the antenna without any mechanical movement. As a result, lower power is required in transmit mode, while signal degradation due to fading in receive mode can be significantly reduced. Depending on the specifications of the phase diversity systems, controllable RF true-time delays are favored over alternative solutions. To investigate the abilities of the SOG varactor concepts for these applications, true time delay phase-shifter prototype has been developed [26] as shown in Fig. 11(c). This phase shifter implementation offers a controllable delay of 110 ps at 1 GHz, with measured  $\mathrm{IIP}_3$  better than +45 dBm. The minimum controllable phase-shift at 1 GHz per dB loss is 150 degrees worst case, a value that is comparable to that of state-ofthe-art MEMS based phase shifters [27], [36].

# III. COMPLEMENTARY BIPOLAR TRANSISTOR INTEGRATION

At present there is an increasing interest in complementary high-frequency SiGe heterojunction-bipolar-transistor (HBT) BiCMOS processes and a few bulk integration schemes have recently been presented [37], [38]. As always in complementary bipolar processes, the speed of the PNP device is limited by the collector contacting via the bulk. The benefit in this respect of the two-sided contacting has been demonstrated in our low-complexity SOG complementary bipolar process.

# A. Schottky Collector Contacting

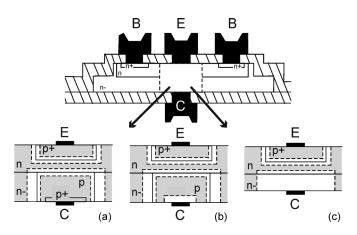

In DIMES SOG bipolar process, the collector is contacted directly under the emitter and several new collector designs have been explored. Instead of the conventional contacting of a lightly-doped collector via a highly-doped region, Schottky col-

Fig. 11. Chip photographs of adaptive RF circuits making use of low-loss high-linearity varactors. (a) Multi-mode multi-band power amplifier with reconfigurable input and output matching network in SOG technology [24]. (b) Schematic and microphotograph of the bandpass tunable filter in SOG technology [25]. (c) Microphotograph of the copper-plated highly linear differential phase-shifter realized in SOG technology [27].

lector contacting can be implemented [7]. This is illustrated in Fig. 12 for the case of Schottky contacting of p-type bipolar transistors. In one case, the lightly-doped p-type collector is retained and contacted by an Al to p-Si Schottky diode. In the other case, the Al metallization is placed directly on the n-type base. The characteristics of these Schottky collector devices were almost identical to the ohmic collector contact devices except for the offset voltage, which becomes very high (even above 0.3 V) for Schottky contacting directly to the base, as shown in Fig. 13. This is determined by the reverse base current, which strongly increases due to the low Schottky barrier height of the contact [39].

Besides their process simplicity, the Schottky contacts also have another advantage because the bipolar devices with im-

Fig. 12. Schematic of different SOG p-type BJT collector contacts: (a) implanted/laser-annealed ohmic, (b) p-Schottky, and (c) n-Schottky collector contacts.

Fig. 13. Measured output characteristics around the offset voltage (at  $I_C=0$ ) for several p-type BJTs with different collector designs. The high offset devices (d, e, f) have a Schottky contact placed either directly on the base or very close to the base.  $I_B=2$ , 4, 6, 8, and 10  $\mu$ A, emitter area  $40\times1~\mu\text{m}^2$  [8].

planted collector contacts suffer from the effects of the residual implantation damage [40]. Depending on the distance to the implant and the type of implant, we observed enhanced junction leakage, increased impact ionization current, and reduced breakdown voltages. These effects were not very pronounced in our devices because we have a process with relaxed dimensions, but, in a downscaled advanced process, the placing of the implanted collector close to the metallurgic collector-base junction may be destructive. This concern is completely taken away by replacing the ohmic contacts with Schottky contacts.

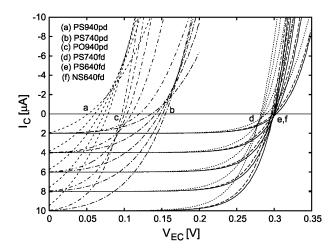

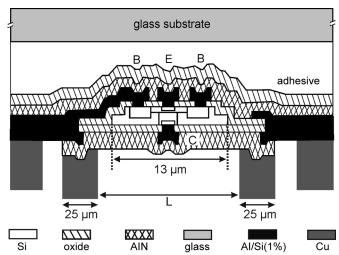

# IV. Aln Thin-Film Heatspreaders

For many SOG devices, heatspreading and heatsinking structures become indispensable at even very low power dissipation levels [10]. For large area devices, thick Cu-plating and direct surface-mounting to a printed-circuit board can provide the necessary heatsinking [41]. In fact, replacing bulk-Si by Cu can be advantageous for reducing the thermal resistance  $R_{TH}$ . However, for circuits of small dimension devices such as high-frequency bipolar transistors, heat transport away from the

Fig. 14. Schematic of a  $20\times1~\mu\mathrm{m}^2$  emitter SOG NPN cooled by AlN and Cu. A 0.8- $\mu$ m-thick AlN on both front- and back-wafer reduces the thermal resistance from 12600 K/W to 7550 K/W and additional Cu-plating brings it down to 3600 K/W.

active device area must preferably be accomplished by a thermally conductive dielectric. For this purpose, we have developed physical-vapor-deposition (PVD) of AlN to form thin-film heatspreaders directly on the SOG devices as shown in Fig. 14 [11].

#### A. AlN Properties

When considering the integration of dielectric heatspreaders, AlN is an obvious choice. It has a large energy bandgap that makes it suitable as an insulator in many situations and a high bulk thermal conductivity of about 270 Wm<sup>-1</sup>K<sup>-1</sup> at room temperature [42]. Moreover, it is compatible with standard silicon technology: it is neither contaminating nor poisonous, and can be both deposited and etched by conventional silicon processing techniques.

The integration of thick heatspreading layers in the front-wafer processing is attractive because they can be deposited just before the gluing procedure and do not require any patterning. Thus, they can in principle be chosen as thick as possible. A limitation on the layer thickness is, however, imposed by the stress since the flatness and integrity of the back-wafer surface after gluing and bulk silicon removal is very sensitive to any stress in the remaining layers. Using a low-stress deposition technique, AlN layers of up to 4  $\mu$ m in thickness were successfully integrated. On the back-wafer it is possible to deposit even thicker layers, but, due to mainly unfavorable etch selectivities, the processing of windows through the AlN to the bondpads entails a trade-off between layer thickness and process complexity.

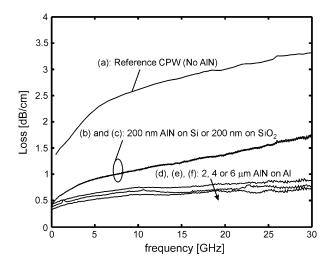

The electrical properties of the AlN layers were found to be suitable both from a DC and RF point of view. The resistivity is of the order of  $10^{13}~\Omega{\rm cm}$  and the dielectric constant falls in the range of 9–11.5. The behavior of AlN at microwave frequencies has been studied by fabricating Al coplanar waveguides on surface-passivated high-resistivity Si wafers. In Fig. 15 the measured losses up to 30 GHz are shown for different configurations of AlN and/or SiO<sub>2</sub>. The results show that the presence of AlN does not introduce additional losses at high frequency, but,

| ВЈТ | AlN front [μm] | AlN back [μm] | <i>L</i> [μm] | <i>R<sub>TH</sub></i> [K/W] |

|-----|----------------|---------------|---------------|-----------------------------|

| 1   | 0              | 0             | no Cu         | 12600                       |

| 2   | 0.8            | 0             | no Cu         | 8800                        |

| 3   | 0.8            | 0.8           | no Cu         | 7550                        |

| 4   | 0.8            | 0.8           | 0             | 3600                        |

| 5   | 0.8            | 0.8           | 18            | 5600                        |

| 6   | 0.8            | 0.8           | 24            | 6500                        |

| 7   | 0.8            | 0.8           | 34            | 6530                        |

$TABLE\ IV$  Thermal Resistances of NPNs With Different Combinations of AlN and Cu Heatspreaders as Applied in Fig. 14

Fig. 15. Measured microwave losses for five different CPWs: (a) CPW on 330 nm SiO<sub>2</sub>; (b) CPW on 200 nm AlN deposited directly on the silicon substrate; (c) CPW on 200 nm AlN deposited on 30 nm SiO<sub>2</sub>; (d) 2  $\mu$ m AlN, (e) 4  $\mu$ m AlN, and (f) 6  $\mu$ m AlN deposited on a CPW as in (a) [11].

on the contrary, depositing AlN reduces the losses. In addition to the conductive properties of the AlN, also the piezoelectric behavior has been examined; crystal morphologies of AlN are known to have strong piezoelectric properties, the presence of which would be undesirable in an RF circuit environment. For a wide range of layer thicknesses, the piezoelectric response of our AlN films was found to be negligible [11].

#### B. AlN Cooling of BJT Circuits

The efficiency of AlN as heatspreader can be seen from the experiment illustrated in Fig. 14, where relatively thin 0.8  $\mu$ m layers are applied to an NPN and also copper-plated blocks are added at different distances from the active device area. In Table IV, the  $R_{TH}$  of the NPN is given as a function of the AlN position and of the distance between two Cu blocks. Each layer of AlN contributes to a strong reduction of  $R_{TH}$ , and, even at 17  $\mu$ m from the center of the active device region, a significant measure of heatsinking by the Cu blocks is achieved.

The thermal conductivity of the AlN thin-films is much lower than the bulk value. It has been estimated here by comparing experimental results to simulations. For the latter, measurement of devices with a wide range of  $R_{TH}$  has been used as a basis to establish reliable thermal [43], [44] and electrothermal [9],

TABLE V THERMAL RESISTANCES EXPERIMENTALLY DETERMINED FOR NPNS WITH DIFFERENT AIN LAYERS DEPOSITED ON THE FRONT-WAFER

| ВЈТ | AlN thickness [μm] | $R_{TH}$ [K/W] |

|-----|--------------------|----------------|

| 1   | 0                  | 19000          |

| 2   | 0.8                | 9000           |

| 3   | 2                  | 7300           |

| 4   | 4                  | 5250           |

[45]–[47] tools. A quite consistent agreement with the experimental results could be achieved by assuming an isotropic AlN thermal conductivity in the range of 20–50 Wm<sup>-1</sup>K<sup>-1</sup> [44]. For a higher accuracy, a more detailed description of the AlN coverage of the device surface topography as well as of the microscopic material properties is needed.

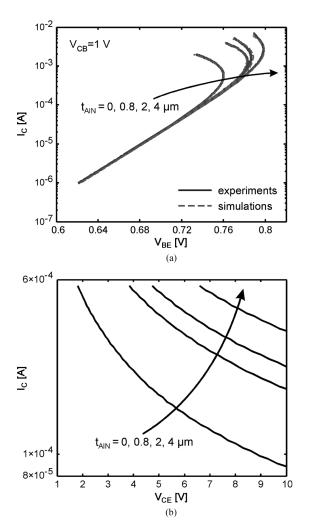

Both experimentally and in the simulations, the AlN induced reduction of  $R_{TH}$  is found to be very significant: a reduction of more than 70% in the value of thermal resistance is obtained by using a 4- $\mu$ m-thick AlN layer on the front-wafer. A series of experimentally determined thermal resistance values are given in Table V and employed in the electrothermal simulations shown in Fig. 16(a). The thicker the AlN layer, the further the onset of thermal instability is pushed to higher dissipation powers. This strongly benefits the safe-operating-area of the transistors as shown in Fig. 16(b).

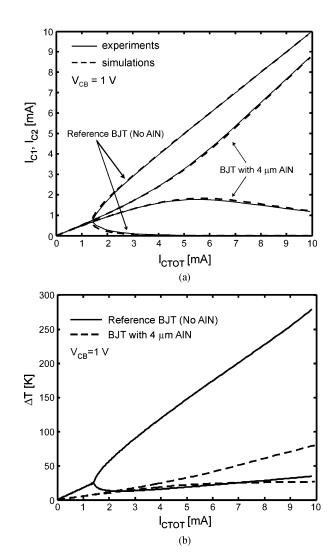

An important function of heatspreaders is to keep critical devices in a circuit at the same temperature. When several transistors in a circuit are operated in parallel, the circuit can suffer from electrothermal instabilities that lead to current hogging by the one transistor while the others switch off [47], [48]. A typical situation is shown in Fig. 17 for an NPN pair where the circuit without AlN cooling is already instable at very low current levels. The addition of a 4- $\mu$ m-thick AlN layer shifts the values of  $R_{TH}$  and the thermal coupling coefficient,  $R_M$ , from 17800 and 2200 K/W to 5000 and 1000 K/W, respectively. Accordingly, the onset of thermal instability is shifted to much higher power dissipation values and the increase in operation temperature of the two transistors is much lower and stays closer together over a much wider current range. For example, for a total current of  $I_{CTOT} = 5$  mA through the two transistors, the difference in operating temperature is more than 130 K without AlN and only a few K with the 4- $\mu$ m-thick layer.

Fig. 16. (a) Experimental and simulated collector current  $I_C$  as a function of the base-emitter voltage  $V_{BE}$  for an NPN covered with AlN layers of different thickness  $t_{AlN}$ . (b) Simulated DC thermal limit of the safe-operating-area of bipolar transistors described in Table V.

For current-controlled BJTs working in parallel, it is known that an increased thermal coupling between the two devices improves the overall electrothermal stability. A figure of merit for the electrothermal robustness of such a circuit is given by the collector current,  $I_{C,crit}$ , at which thermal instability appears. In a current controlled two-emitter-finger device, the onset of the current bifurcation is described by the relationship [48], [49]

$$I_{C,crit} \propto \frac{1}{V_{CE}(R_{TH} - R_M)} \tag{6}$$

where  $V_{CE}$  is the collector-emitter voltage. For the situation illustrated in Fig. 17, the difference  $R_{TH} - R_M$  drops from 15600 K/W to 4000 K/W when the AIN heatspreader is added.

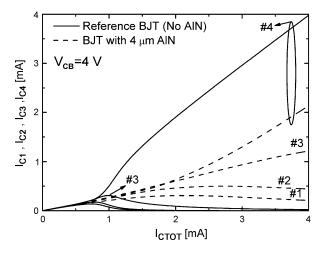

For circuits of elementary transistors connected in parallel, the electrothermal feedback is very susceptible to all the small differences that are in practice always present in "identical" devices. For example, the surroundings of the outer fingers are often designed differently from the inner fingers in which case the outer fingers will show the most deviating behavior, but also more subtle differences such as an asymmetry with respect to the position of the connecting metal tracks can cause significant

Fig. 17. (a) Measured (solid lines) and simulated (dashed lines) collector currents, and (b) simulated increase of temperature above ambient of the individual transistors of a pair operated in parallel as a function of the total collector current for devices with and without a 4- $\mu$ m-thick layer of AlN. For these two identical NPN BJTs the emitters are 42.5  $\mu$ m apart and separated by otherwise thermally isolating materials.

differences in thermal resistance. In Fig. 18, a circuit of four BJTs operating in parallel is considered. The four emitters and base terminals are all connected, while the collectors are contacted individually and the collector current of each transistor is measured. The circuit without extra cooling is already instable at very low current levels. The outer transistor #4 hogs 50% of the total collector current at  $I_{CTOT}=1\,\mathrm{mA}$ . For a device with a 4- $\mu$ m-thick layer of AlN added, the operating temperatures of the four devices become closer and BJT #4 takes only half of the total current at  $I_{CTOT}=3.7\,\mathrm{mA}$ . Thus, the reliability of the overall circuit is significantly improved.

# V. FUTURE POTENTIALS

# A. Potentials for HF SiGe HBT Fabrication

The future of Si-based high-speed bipolar transistors is strongly influenced by two other semiconductor developments. On one hand, SiGe HBTs must compete in speed with III-V HBTs, which in InP have already reached an operation

Fig. 18. Measured collector currents of the individual transistors of a set of four operated in parallel as a function of the total collector current for devices with (dashed lines) and without (solid lines) a 4- $\mu$ m-thick layer of AlN. The neighboring emitters are 12.5  $\mu$ m apart and separated by otherwise thermally isolating materials.

frequency of 1 THz [50]. This is three times the speed demonstrated in SiGe devices for room temperature operation [51]. On the other hand, SiGe bipolars have always had the advantage of being compatible with CMOS, but as the speed domain of pure CMOS is ever increasing, the cost and versatility with which SiGe HBTs can be integrated will continue to be important considerations when making process development choices.

The downscaling of SiGe HBT vertical doping profiles needed to reach  $f_T$ 's way above 500 GHz has been theoretically predicted [52], but the concomitant downscaling of the series/contact resistances and capacitances is technologically very challenging. Obviously, the two-sided contacting can offer some relaxation of the device design compromises. With the aligning of the collector contact under the emitter, the  $R_C$  can be minimized. For a doped collector, the minimum  $R_C$  is determined by how well the doping technology can be downscaled. For low-ohmic contacting, high surface doping must be accommodated. With Schottky collector contacting,  $R_C$  can be entirely eliminated and reduction in transit time and storage time also gives a speed advantage [53], [54]. The surface recombination velocity at the metal-Si interface becomes the element that can limit the current handling capability. The metal will in first instance be chosen to have a Schottky barrier-height high enough to enable contacting as close as possible to the high-doped base while still maintaining good collector-base diode characteristics. The proximity of the metal contact to the high-doped base may have a benefit for cutting off collector-current (non-local) avalanching. For high frequency (HF) analog applications, any resulting high offset voltage is not problematic, so the optimization for high breakdown voltages will determine the collector design.

The future SiGe HBTs may have to be integrated with SOI fully-depleted CMOS [1] with Si top-layers of about 100 nm or less. In this case, the collector design is the key issue. A fully-depleted collector has been proposed in [55], which trades  $f_T$  for base-collector breakdown voltage. If SOI CMOS were to be extended to a substrate transfer implementation, the integration of

SiGe HBTs with two-sided contacting becomes straightforward. Even for ultra-thin SOI below 50-nm-thick, the vertical dimensions are large enough to be able to accommodate a Schottky collector contact placed directly on the base.

#### B. Technologies for Two-Sided Contacting

Even though the SOG substrate transfer process is more evolutionary than revolutionary, from a production point of view it involves process modules that are not very widely used. In this respect it would be more attractive to achieve the two-sided contacting by micromachining of cavities to locally remove the substrate below the vital circuit regions. In silicon this would almost always imply the use of SOI wafers so that the BOX can be used as etch-stop. In III-V realizations, however, etch-stop layers can be grown along with the device layer stack. The main disadvantages of the micromachining version, as compared to the SOG solution, lie in the inferior accuracy of the patterning in the cavities. For large area back-wafer contacts, such as those needed for varactors, this does not become a serious limitation. Nevertheless, the size of the circuit will always be limited by membrane stability issues. This makes SOG the more flexible approach to two-sided contacting.

For the SOG IC-processing technology, the individual processing modules, including the STT and the laser annealing [56], have all been production-proven to some extent. The main concerns are connected to the stress relief experienced after gluing and silicon removal. In all our processes, the Si is thinned to around a micrometer or less and, at this thickness, Si is strong but bendable. However, topography introduced by trenching of the Si and thick metal stacks can induce high-stress points that break when the bulk-Si is removed. This does not necessarily cause direct damage of the Si devices, but will readily lead to cracks that expose the glue and front-wafer device-regions during Si-removal. This, together with bowing of the wafer, is very detrimental to the further processing of the back-wafer. In particular, the wafer-stepper alignment has need of a flat backwafer surface [57]. Most of these stress-related problems can be minimized by using low-stress materials and well-chosen design rules for the circuit integration. Moreover, the choice of glass wafer is extremely important: a more rigid/thicker glass substrate will reduce stress-relief induced cracking. Also, choosing glass with a thermal expansion coefficient close to that of Si is beneficial. We have obtained very reliable results with 700- $\mu$ m -thick glass wafers and a glue thickness in the 5–10  $\mu$ m range. Nevertheless, cracking has limited the AlN thickness that we can integrate reliably in the front-wafer processing to 4  $\mu$ m.

The SOI wafers used in the SOG process are more expensive and less production-proven with respect to quality than bulk Si. However, the SOG gives a very significant reduction of processing steps with respect to a comparable bulk process and this compensates for the extra wafer costs. The very low device and circuit RC parasitics also lower the costs of establishing reliable design kits: as an example, an SOG varactor-circuit design-kit can be found in [58]. Moreover, the quality of the SOI wafers has also become an industrial focus point, particularly for the thin Si SOI needed for future fully-depleted CMOS. The SOG developments are in line with the targets of industrial consortiums dedicated to SOI CMOS development. The flexibility of the SOG process with respect to the back-wafer processing

would be considerably increased if the thermal budget was limited by the front-wafer metallization scheme and not by the glue. Forming-gas alloying could then also be performed at 400 °C on the back-wafer. In the presented processes all junctions are H-passivated in the front-wafer processing, but otherwise this could become a reliability concern.

With respect to packaging, already established packaging procedures can be used if the quality of the glass wafer is chosen to be able to withstand the same treatment as a Si-wafer. This is in contrast to the situation for RF-MEMS, where fundamentally new packaging strategies are being developed when moving parts have to be protected and not impeded in their mechanical behavior by the package. For SOG, the choice of substrate quality, which can also mean replacing glass by some other sort of material, can be seen as a matter of cost.

#### VI. CONCLUSION

This work demonstrates that unique technology platforms in research environments can be an attractive incubator for new device and circuit developments. Among other things, the access to two-side contacted SOG has boosted the theoretical understanding of electrothermal bipolar circuit behavior, given the incentive to introduce deposited AlN as a new device-level heatspreading material, and provided an experimental basis for the development of new and potent varactor circuit-topologies. These are all results that can be adopted by industry also in other technology platforms.

The two-sided contacting offers a very effective means of reducing the RC parasitics, which is one of the prerequisites for efficiently exploiting silicon in RF/microwave applications and carrying it into the terahertz age. As compared to micromachined versions of two-sided contacting, the SOG technology offers much more flexibility and, in contrast to disruptive technologies such as RF MEMS, the SOG option contains no fundamentally new manufacturability challenges.

# ACKNOWLEDGMENT

The authors would like to thank the staff of DIMES cleanrooms and measurement rooms for their continual support.

#### REFERENCES

- [1] I. Z. Mitrovic, O. Buiu, S. Hall, D. M. Bagnall, and P. Ashburn, 'Review of SiGe HBTs on SOI," Solid-State Electron., vol. 49, pp. 1556-1567, 2005.

- [2] M. Spirito, F. De Paola, L. K. Nanver, E. Valletta, B. Rong, B. Rejaei, L. C. N. de Vreede, and J. N. Burghartz, "Surface-passivated high-resistivity silicon as a true microwave substrate," IEEE Trans. Microw. Theory Tech., vol. 53, no. 7, pp. 2340–2347, 2005.

- [3] N. P. Pham, P. M. Sarro, K. T. Ng, and J. N. Burghartz, "IC-compatible two-level bulk micromachining process module for RF silicon technology," *IEEE Trans. Electron Devices*, vol. 48, no. 8, pp. 1756–1764,

- [4] R. Dekker, P. G. M. Baltus, M. van Deurzen, W. T. A. van der Einden, H. G. R. Maas, and A. Wagemans, "An ultra low-power RF bipolar technology on glass," in IEDM Tech. Dig., 1997, pp. 921-923.

- [5] R. Dekker, P. G. M. Baltus, and H. G. R. Maas, "Substrate transfer for RF technologies," IEEE Trans. Electron Devices, vol. 50, no. 3, pp. 747-757, 2003.

- [6] M. Rodwell, Q. Lee, D. Mensa, J. Guthrie, S. C. Martin, R. P. Smith, R. Pullela, B. Agarwal, S. Jaganathan, T. Mathew, and S. Long, "Transferred-substrate HBT integrated circuits," Solid-State Electron., vol. 43, pp. 1489-1495, 1999.

- [7] L. K. Nanver, N. Nenadović, V. d'Alessandro, H. Schellevis, H. W. van Zeijl, R. Dekker, D. B. de Mooij, V. Zieren, and J. W. Slootboom, "A back-wafer contacted silicon-on-glass integrated bipolar process—Part I: The conflict electrical versus thermal isolation," IEEE Trans. Electron Devices, vol. 51, no. 1, pp. 42-50, 2004.

- [8] G. Lorito, L. K. Nanver, and N. Nenadović, "Offset voltage of Schottky-collector silicon-on-glass vertical PNP's," in Proc. IEEE BCTM, 2005, pp. 22–25.

[9] N. Nenadović, V. d'Alessandro, L. La Spina, N. Rinaldi, and L. K.

- Nanver, "Restabilizing mechanisms after the onset of thermal instability in bipolar transistors," *IEEE Trans. Electron Devices*, vol. 53, no. 4, pp. 643-653, 2006.

- [10] N. Nenadović, V. d'Alessandro, L. K. Nanver, F. Tamigi, N. Rinaldi, and J. W. Slotboom, "A back-wafer contacted silicon-on-glass integrated bipolar process-Part II: A novel analysis of thermal breakdown," IEEE Trans. Electron Devices, vol. 51, no. 1, pp. 51–62, 2004.

- [11] L. La Spina, E. Iborra, H. Schellevis, M. Clement, J. Olivares, and L. K. Nanver, "Aluminum nitride for heatspreading in RF IC's," Solid-State

- Electron., vol. 52, no. 9, pp. 1359–1363, 2008. [12] J. B. Muldavin and G. M. Rebeiz, "High-isolation CPW MEMS shunt switches-Part 1: Modeling," IEEE Trans. Microw. Theory Tech., vol. 48, pp. 1045–1052, Jun. 2000.

- [13] L. Dussopt and G. M. Rebeiz, "Intermodulation distortion and power handling in RF MEMS switches, varactors and tunable filters," IEEE Trans. Microw. Theory Tech., vol. 51, pp. 1247–1256, Apr. 2003.

- [14] K. Entesari and G. M. Rebeiz, "A 12-18-GHz three pole RF MEMS tunable filter," IEEE Trans. Microw. Theory Tech., vol. 53, pp. 2566-2571, Aug. 2005.

- Y. Lu, L. P. B. Katehi, and D. Peroulis, "High-power MEMS varactor and impedance tuners for millimeter-wave applications," IEEE Trans. Microw. Theory Tech., vol. 53, pp. 3672-3678, Nov. 2005.

- [16] D. Girbau, N. Otegi, L. Pradell, and A. Lazaro, "Generation of third and higher-order intermodulation products in MEMS capacitors, and

- their effects," in *Proc. Eur. Microw. Conf.*, Oct. 2005, pp. 593–596. [17] D. R. Chase, L. Y. Chen, and R. A. York, "Modeling the capacitive nonlinearity in thin-film BST varactors," IEEE Trans. Microw. Theory Tech., vol. 53, pp. 3215-3220, Oct. 2005.

- [18] J. S. Fu, X. A. Zhu, D. Y. Chen, J. D. Phillips, and A. Mortazawi, "A linearity improvement technique for thin-film barium strontium titanate capacitors," in *IEEE MTT-S Int. Microw. Symp. Dig.*, San Francisco, CA, Jun. 2006, pp. 560–563.

- [19] R. G. Meyer and M. L. Stephens, "Distortion in variable-capacitance diodes," IEEE J. Solid-State Circuits, vol. SC-10, pp. 47–55, Feb. 1975.

- K. Buisman, L. C. N. de Vreede, L. E. Larson, M. Spirito, A. Akhnoukh, T. L. M. Scholtes, and L. K. Nanver, "Distortion-free' varactor diode topologies for RF adaptivity," in IEEE MTT-S Int.

- Microw. Symp. Dig., 2005, pp. 157–160. [21] C. Huang, K. Buisman, L. K. Nanver, F. Sarubbi, M. Popadić, T. L. M. Scholtes, H. Schellevis, L. E. Larson, and L. C. N. de Vreede, "A 67 dBm  $OIP_3$  multi-stacked junction varactor," *IEEE Microw. Wireless* Compon. Lett., vol. 18, no. 11, pp. 749-751, Nov. 2008.

- [22] C. Huang, K. Buisman, M. Marchetti, L. K. Nanver, F. Sarubbi, M. Popadić, T. L. M. Scholtes, H. Schellevis, L. E. Larson, and L. C. N. de Vreede, "Ultra linear low-loss varactor diode configurations for adaptive RF systems," IEEE Trans. Microw. Theory Tech., vol. 57, no. 1, pp. 205–215, Jan. 2009.

- [23] C. Huang, L. C. N. de Vreede, F. Sarubbi, M. Popadić, K. Buisman, J. Qureshi, M. Marchetti, A. Akhnoukh, T. L. M. Scholtes, L. E. Larson, and L. K. Nanver, "Enabling low-distortion varactors for adaptive transmitters," IEEE Trans. Microw. Theory Tech., vol. 56, pp. 1149-1163, May 2008.

- [24] W. C. Edmund, Y. Lin, X. D. Liu, L. C. N. de Vreede, L. E. Larson, M. Spirito, M. J. Pelk, K. Buisman, A. Akhnoukh, A. de Graauw, and L. K. Nanver, "Adaptive multi-band multi-mode power amplifier using integrated varactor-based tunable matching networks," IEEE J. Solid-State Circuits, vol. 41, no. 9, pp. 2166-2176, Sep. 2006.

- [25] K. Buisman, L. C. N. de Vreede, L. E. Larson, Y. Lin, X. D. Liu, and L. K. Nanver, "A monolithic low-distortion low-loss silicon-on-glass

- L. R. Nailvei, A indinition towards that now-loss sincon-on-glass varactor-tuned filter with optimized biasing," *IEEE Microw. Wireless Compon. Lett.*, vol. 18, no. 11, pp. 749–751, Nov. 2006.

[26] K. Buisman, C. Huang, A. Akhnoukh, M. Marchetti, L. C. N. de Vreede, L. E. Larson, and L. K. Nanver, "Varactor topologies for RF adaptivity with improved power handling and linearity," in IEEE MTT-S Int. Microw. Symp. Dig., 2007, pp. 319-322

- [27] J. H. Qureshi, S. Kim, K. Buisman, C. Huang, M. J. Pelk, A. Akhnoukh, L. E. Larson, L. K. Nanver, and L. C. N. de Vreede, "A low-loss compact linear varactor based phase-shifter," in IEEE Radio Frequency Integrated Circuits (RFIC) Symp., Honolulu, HI, Jun. 2007, pp. 453-456.

- [28] D. A. Neamen, Semiconductor Physics & Devices, 2nd ed. Chicago, II.: Irwin 1997

- [29] J. L. Hudgins, G. S. Simin, and M. A. Khan, "A new assessment of the use of wide bandgap semiconductors and the potential for GaN," in *IEEE Power Electronics Specialists Conf.*, Cairns, Jun. 2002, pp. 1474–1752.

- [30] V. Gonda, A. Burtsev, T. L. M. Scholtes, and L. K. Nanver, "Near-ideal implanted shallow-junction diode formation by excimer laser annealing," in *Proc. IEEE RTP*, 2005, vol. 13, pp. 93–100.

- [31] V. Gonda, S. Liu, T. L. M. Scholtes, and L. K. Nanver, "Electrical characterization of residual implantation-induced defects in the vicinity of laser-annealed implanted ultrashallow junctions," in MRS Symp. Dig., 2006, vol. 912, pp. 173–178.

- 2006, vol. 912, pp. 173–178.

[32] M. Spirito, M. J. Pelk, F. van Rijs, S. J. C. H. Theeuwen, D. Hartskeerl, and L. C. N. de Vreede, "Active harmonic load-pull for on-wafer out-of-band device linearity optimization," *IEEE Trans. Microw. Theory Tech.*, vol. 54, pp. 4225–4236, Dec. 2006.

- [33] G. M. Rebeiz, *RF MEMS: Theory, Design and Technology*. Hoboken, NJ: Wiley, 2003.

- [34] D. Girbau, N. Otegi, L. Pradell, and A. Lazaro, "Study of intermodulation in RF MEMS variable capacitors," *IEEE Trans. Microw. Theory Tech.*, vol. 54, pp. 1120–1130, Mar. 2006.

- [35] J. S. Fu, X. A. Zhu, J. D. Phillips, and A. Mortazawi, "Improving linearity of ferroelectric-based microwave tunable circuits," *IEEE Trans. Microw. Theory Tech.*, vol. 55, pp. 354–360, Feb. 2007.

[36] F. Ellinger, R. Vogt, and W. Bachtold, "Ultra compact, low loss, var-

- [36] F. Ellinger, R. Vogt, and W. Bachtold, "Ultra compact, low loss, varactor tuned phase shifter MMIC at C-band," *IEEE Microw. Wireless Compon. Lett.*, vol. 11, no. 3, pp. 104–105, Mar. 2001.

[37] D. Knoll, B. Heinemann, Y. Yamamoto, H. E. Wulf, and D. Schmidt,

- [37] D. Knoll, B. Heinemann, Y. Yamamoto, H. E. Wulf, and D. Schmidt, "PNP SiGe:C optimization in a low-cost CBiCMOS process," in *Proc. IEEE BCTM*, 2007, pp. 30–33.

- [38] J. Duvernay, F. Brossard, G. Borot, L. Boissonnet, B. Vandelle, L. Rubaldo, F. Deléglise, G. Avenier, P. Chevalier, B. Rauber, D. Dutartre, and A. Chantre, "Development of a self-aligned PNP HBT for a complementary thin-SOI SiGeC BiCMOS technology," in *Proc. IEEE BCTM*, 2007, pp. 34–37.

- [39] M. J. Kumar and C. L. Reddy, "Realising wide bandgap P-SiC-emitter lateral heterojunction bipolar transistors with low collector-emitter offset voltage and high current gain: A novel proposal using numerical simulation," *IEE Proc. Circuits Devices Syst.*, vol. 151, no. 5, pp. 399–405, 2004.

- [40] G. Lorito, V. Gonda, S. Liu, T. L. M. Scholtes, H. Schellevis, and L. K. Nanver, "Reliability issues related to laser-annealed implanted backwafer contacts in bipolar silicon-on-glass processes," in *Proc. IEEE MIEL*, 2006, vol. 2, pp. 369–372.

[41] N. Nenadović, V. Cuoco, S. J. C. H. Theeuwen, H. Schellevis, G. Spier-

- [41] N. Nenadović, V. Cuoco, S. J. C. H. Theeuwen, H. Schellevis, G. Spierings, A. Griffo, M. Pelk, L. K. Nanver, R. F. F. Jos, and J. W. Slotboom, "RF power silicon-on-glass VDMOSFETs," *IEEE Electron Device Lett.*, vol. 25, no. 6, pp. 424–426, 2004.

- [42] K. Watari and S. L. Shinde, "High thermal conductivity materials," *MRS Bulletin*, pp. 440–441, Jun. 2001.

[43] L. La Spina, I. Marano, V. d'Alessandro, H. Schellevis, and L. K.

- [43] L. La Spina, I. Marano, V. d'Alessandro, H. Schellevis, and L. K. Nanver, "Aluminium-nitride thin-film heatspreaders integrated in bipolar transistors," in *Proc. IEEE EuroSimE*, 2008, pp. 99–103.

- [44] S. Russo, L. La Spina, V. d'Alessandro, N. Rinaldi, and L. K. Nanver, "Thermal design of fully-isolated bipolar transistors," in *Proc. IEEE THERMINIC*, 2008, pp. 101–105.

- [45] L. La Spina, N. Nenadović, V. d'Alessandro, L. K. Nanver, and N. Rinaldi, "FEAT—A simulation tool for electrothermal analysis of multifinger bipolar transistors," in *Proc. IEEE EUROCON*, 2005, pp. 879–882.

- [46] V. d'Alessandro, L. La Spina, N. Rinaldi, and L. K. Nanver, "SOA reduction due to combined electrothermal and avalanche effects in multifinger bipolar transistors," in *Proc. IEEE BCTM*, 2008, pp. 92 89

- [47] L. La Spina, N. Nenadović, V. d'Alessandro, F. Tamigi, N. Rinaldi, L. K. Nanver, and J. W. Slotboom, "Thermally induced current bifurcation in bipolar transistors," *Solid-State Electron.*, vol. 50, pp. 877–888, 2006.

- [48] N. Rinaldi and V. d'Alessandro, "Theory of electrothermal behavior of bipolar transistors: Part II—Two-finger devices," *IEEE Trans. Electron Devices*, vol. 52, no. 9, pp. 2022–2033, 2005.

- [49] W. Liu, "Thermal coupling in 2-finger heterojunction bipolar transistors," *IEEE Trans. Electron Devices*, vol. 42, no. 6, pp. 1033–1038, 1005

- [50] F. Schwierz and J. J. Liou, "RF transistors: Recent developments and roadmap toward terahertz applications," *Solid-State Electron.*, vol. 51, no. 8, pp. 1079–1091, 2007.

- [51] J. Yuan, R. Krithivansan, J. D. Cressler, M. H. Ahlgren, and A. J. Joseph, "On the frequency limits of SiGe HBTs for terahertz applications," in *Proc. IEEE BCTM*, 2007, pp. 22–25.

- [52] Y. Shi and G. Niu, "2-D analysis of device parasitics for 800/1000 GHz  $\rm f_T/f_{max}$  SiGe HBT," in *Proc. IEEE BCTM*, 2005, pp. 252–255.

- [53] M. J. Kumar and D. V. Rao, "A new lateral PNM Schottky collector bipolar transistor on SOI for non saturating VLSI logic design," *IEEE Trans. Electron Devices*, vol. 49, no. 6, pp. 1070–1072, 2002.

- [54] O. Nur and M. Willander, "The high-speed performance of p-Si/n-Si<sub>1-x</sub>Ge<sub>x</sub>/CoSi<sub>2</sub> Schottky collector HBTs," *Microelectron. J.*, vol. 25, pp. 399–406, 1994.

- [55] G. Avenier, T. Schwartzmann, P. Chevalier, B. Vandelle, L. Rudbaldo, D. Dutartre, L. Boissonnet, F. Saguin, R. Pantel, S. Fregonese, C. Maneux, T. Zimmer, and A. Chantre, "A self-aligned vertical HBT for thin SOI SiGeC BiCMOS," in *Proc. IEEE BCTM*, 2005, pp. 128–131.

- [56] V. Privitera, A. La Magna, C. Spinella, G. Fortunato, L. Mariucci, M. Cuscunà, C. M. Camalleri, A. Magri, G. La Rosa, B. G. Svensson, E. V. Monakhov, and F. Simon, "Integration of melting excimer laser annealing in power MOS technology," *IEEE Trans. Electron Devices*, vol. 54, no. 4, pp. 852–860, 2007.

- [57] H. W. van Zeijl and J. Slabbekoorn, "Front- to back-wafer overlay accuracy in substrate transfer technologies," in *Proc. Int. Conf. Semiconductor Technology*, 2001, pp. 365–367.

- [58] ADS library, "Ultra-low distortion varactor stacks," [Online]. Available: www.dimes.tudelft.nl

Lis K. Nanver (S'80–M'83) received the M.Sc. degree in physics in 1979 from the University of Aarhus, Aarhus, Denmark. In 1982 she received the Dr.ing. degree from the Ecole Nationale Supérieure des Télécommunications, Paris, France, where she worked on the simulation of CCD structures. In 1987 she received the Ph.D. degree from the Delft University of Technology, Delft, The Netherlands, where she developed a medium-frequency BIFET process.

In 1988 she joined the Delft Institute for Microsystems and Nanoelectronics (DIMES) IC Process Research Sector as Bipolar Process Research Manager. She became Associate Professor and later Professor with the Faculty of Electrical Engineering, Mathematics and Computer Science, Delft University of Technology, detached at DIMES Technology Center in 1994 and 2001, respectively. Within the Laboratory of Electrical Components, Technology and Materials, she manages the research on the integration of silicon devices, mainly for RF, microwave, or smart sensor applications. This research involves technologies such as epitaxy by chemical-vapor or metal-induced solid-phase deposition, excimer laser processing

Prof. Nanver has served on the committees of ESSDERC and BCTM.

and substrate transfer techniques.

**Hugo Schellevis** received a degree in chemical engineering in 1986 from the Institute of Technology in Amsterdam, The Netherlands. In 1996, he received the M.Sc. degree in chemical engineering from the University of Amsterdam, The Netherlands.

In 1988, he joined the Delft Institute of Microsystems and Nanoelectronics (DIMES) IC Process Research Sector, Delft University of Technology, as a process engineer. Currently, his main research interests are the development of metallization processes and substrate transfer technology.

**Tom L. M. Scholtes** received the HBO engineering degree in chemistry in Sittard in 1984, the HTS engineering degree in applied physics in Heerlen 1988, and a post HBO degree in environmental technology in Dordrecht 1994.

He first worked with the consultancy bureau Cauberg Huygen from 1988 to 1990. He then joined the Laboratory of Optics, Faculty of Applied Physics, Delft University of Technology in 1990 where he worked on the processing of InP-InGaAsP devices. In 1996 he joined the Delft Institute for

Microsystems and Nanoelectronics (DIMES) as process technologist in the IC Process Research Sector attached to the Laboratory of Electrical Components, Technology and Materials, Faculty of Electrical Engineering, Mathematics and Computer Science, Delft University of Technology. His interests are technologies such as advanced CVD epitaxy, ion implantation and excimer laser annealing for the fabrication of silicon-based semiconductor devices.

Luigi La Spina (S'06) received the Laurea degree in electronics engineering from the University of Naples Federico II, Italy, in 2004. In January 2005 he joined the Faculty of Electrical Engineering, Mathematics and Computer Science, Delft University of Technology, The Netherlands, where he received the Ph.D. degree in 2009. He was working within the Laboratory of Electronic Components and Technology Materials (ECTM) in association with Delft Institute of Microsystems and Nanoelectronics (DIMES).

His research interests include electrothermal analysis of bipolar junction transistors (BJTs), thermal properties of thin-film materials, and heat conduction in micro- and nanoscale structures.

Miloš Popadić was born in Belgrade, Serbia, in 1981. He received the M.Sc. degree in electrical engineering from the University of Belgrade, Belgrade, in 2005. He is currently working toward the Ph.D. degree at the Delft University of Technology, Delft, The Netherlands.

Since 2005, he has been with the Laboratory of Electronic Components, Technology and Materials, Faculty of Electrical Engineering, Mathematics and Computer Science, Delft University of Technology, associated with Delft Institute of Microsystems and

Nanoelectronics (DIMES). He is involved in the investigation of the electrical properties of contacts and ultrashallow junctions in silicon technology.

**Gianpaolo Lorito** was born in Salerno, Italy, in 1974. He graduated *cum laude* in electronics engineering at the University of Naples Federico II, Italy. He carried out his master thesis at Delft University of Technology, in Delft, The Netherlands, studying the offset voltage in silicon-on-glass PNP bipolar transistors.

Since 2006, he has been working as Ph.D. candidate in the Laboratory of Electronic Components and Technology Materials (ECTM), Faculty of Electrical Engineering, Mathematics and Computer Sci-

ence, Delft University of Technology, The Netherlands, in association with Delft Institute of Microsystems and Nanoelectronics (DIMES). He is fully involved in the design, fabrication and electrical characterization of silicon-on-glass SiGe HBTs for high frequency applications.

**Koen Buisman** (S'05) received the M.Sc. degree in microelectronics from Delft University of Technology, Delft, The Netherlands, in 2004, and is currently working toward the Ph.D. degree at Delft University of Technology.

Since 2004, he has been with the Delft Institute of Microsystems and Nanoelectronics (DIMES), Delft University of Technology. He was involved in the development of a pulsed DC & RF measurement system, an active harmonic load-pull system and the development of a custom in-house DIMES

technology for high performance "distortion-free" varactors. His research interests are varactors for RF adaptivity, nonlinear device characterization and compact modeling of heterojunction bipolar transistors. He has authored or coauthored over 20 papers.

Francesco Sarubbi was born in Rome, Italy, in 1977. He received the M.Sc. degree (with honors) in electronics engineering from the University of Naples Federico II, Naples, Italy, in 2004, after having completed his Master's thesis at the Department of Microelectronics and Information Technology of the Royal Institute of Technology, Stockholm, Sweden, on the electrical characterization and modeling of heavy doping effects in 4H-silicon carbide.